|

byteman

1.3 (Build #225)

Bitstream relocation and manipulation tool

|

|

byteman

1.3 (Build #225)

Bitstream relocation and manipulation tool

|

#include "XilinxUltraScale.h"

Public Member Functions | |

| void | assembler (std::string, std::string) |

| void | assemblerAsmTo (std::ifstream &, std::ofstream &) |

| void | assemblerAsmToBin (std::ifstream &, std::ofstream &) |

| void | assemblerAsmToBit (std::ifstream &, std::ofstream &) |

| void | assemblerParseHeader (std::ifstream &) |

| void | blank (std::string) |

| void | change (std::string) |

| void | deviceHelp () |

| void | disassemblerBinToAsm (std::string, std::ifstream &, std::ofstream &) |

| void | disassemblerBitToAsm (std::ifstream &, std::ofstream &) |

| void | disassemblerToAsm (std::ifstream &, std::ofstream &) |

| void | disassemblerWriteHeader (std::ofstream &) |

| void | ensureInitializedBitstreamArrays () override |

| int | getDeviceByIDCODE (int) override |

| int | getDeviceByIDCODEorThrow (int) override |

| int | getDeviceByName (std::string) override |

| int | getDeviceByNameOrThrow (std::string) override |

| std::string | getFrameType (int, int, int) override |

| void | initFabric () |

| void | initializeResourceStringParameters () override |

| void | merge (XilinxUltraScale *, std::string, Rect2D, Coord2D) |

| void | outputBitstreamEmptySLRHeaderSequence (std::ofstream &, int, bool, Endianness) override |

| void | outputBitstreamEmptySLRWrapUpSequence (std::ofstream &, int, bool, Endianness) override |

| void | outputBitstreamGlobalFooterSequence (std::ofstream &, bool, Endianness) override |

| void | outputBitstreamGlobalHeaderSequence (std::ofstream &, bool, Endianness) override |

| Written by outputBitstreamSLRHeaderAfterBitstreamSequence(), outputBitstreamEmptySLRHeaderSequence() and used by outputBitstreamSLRWrapUpSequence(), outputBitstreamEmptySLRWrapUpSequence() More... | |

| void | outputBitstreamSLRFooterBitstreamSequence (std::ofstream &, int, bool, Endianness) override |

| void | outputBitstreamSLRHeaderAfterBitstreamSequence (std::ofstream &, int, bool, Endianness) override |

| void | outputBitstreamSLRHeaderBitstreamSequence (std::ofstream &, int, bool, Endianness) override |

| void | outputBitstreamSLRWrapUpSequence (std::ofstream &, int, bool, Endianness) override |

| void | readBitstream (std::string) |

| void | setDevice (int, std::string="") override |

| void | setDeviceByIDCODEOrThrow (int) override |

| void | setDeviceByNameOrThrow (std::string) override |

| void | setDeviceByPartNameOrThrow () override |

| void | test (bool, bool, uint32_t) |

| void | writeBitstream (std::string, std::string, Rect2D) |

| XilinxUltraScale () | |

| virtual | ~XilinxUltraScale () |

Public Member Functions inherited from CommonDevice2D Public Member Functions inherited from CommonDevice2D | |

| CommonDevice2D () | |

| void | region (std::string, Rect2D) |

| virtual | ~CommonDevice2D () |

Public Member Functions inherited from CommonDevice Public Member Functions inherited from CommonDevice | |

| CommonDevice () | |

| void | log (std::string message) |

| void | printMessage (std::string message) |

| void | warn (std::string message) |

| virtual | ~CommonDevice () |

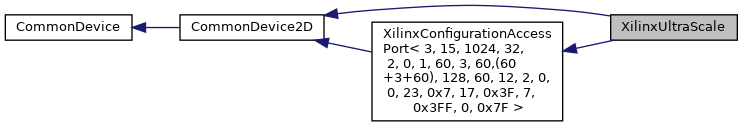

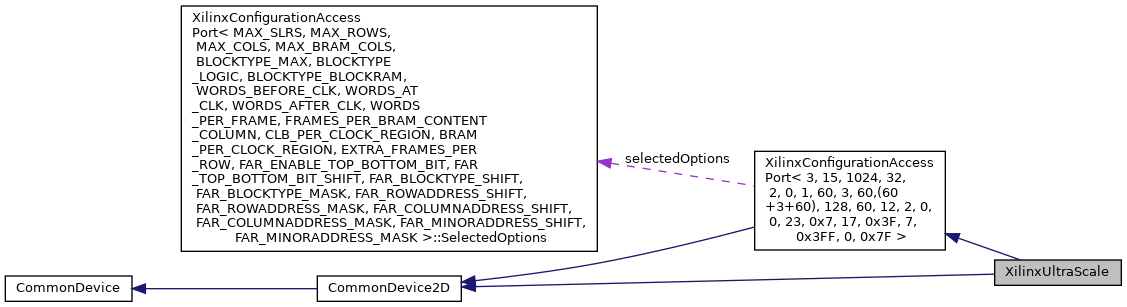

Public Member Functions inherited from XilinxConfigurationAccessPort< 3, 15, 1024, 32, 2, 0, 1, 60, 3, 60,(60+3+60), 128, 60, 12, 2, 0, 0, 23, 0x7, 17, 0x3F, 7, 0x3FF, 0, 0x7F > Public Member Functions inherited from XilinxConfigurationAccessPort< 3, 15, 1024, 32, 2, 0, 1, 60, 3, 60,(60+3+60), 128, 60, 12, 2, 0, 0, 23, 0x7, 17, 0x3F, 7, 0x3FF, 0, 0x7F > | |

| XilinxConfigurationAccessPort () | |

| virtual | ~XilinxConfigurationAccessPort () |

Additional Inherited Members | |

Public Types inherited from XilinxConfigurationAccessPort< 3, 15, 1024, 32, 2, 0, 1, 60, 3, 60,(60+3+60), 128, 60, 12, 2, 0, 0, 23, 0x7, 17, 0x3F, 7, 0x3FF, 0, 0x7F > Public Types inherited from XilinxConfigurationAccessPort< 3, 15, 1024, 32, 2, 0, 1, 60, 3, 60,(60+3+60), 128, 60, 12, 2, 0, 0, 23, 0x7, 17, 0x3F, 7, 0x3FF, 0, 0x7F > | |

| enum class | MergeOP |

Definition at line 31 of file XilinxUltraScale.h.

| XilinxUltraScale::XilinxUltraScale | ( | ) |

Definition at line 31 of file XilinxUltraScale.cpp.

|

virtual |

Definition at line 36 of file XilinxUltraScale.cpp.

| void XilinxUltraScale::assembler | ( | std::string | , |

| std::string | |||

| ) |

Definition at line 32 of file XUS_Assembler.cpp.

References str::iff::stringEndsWith().

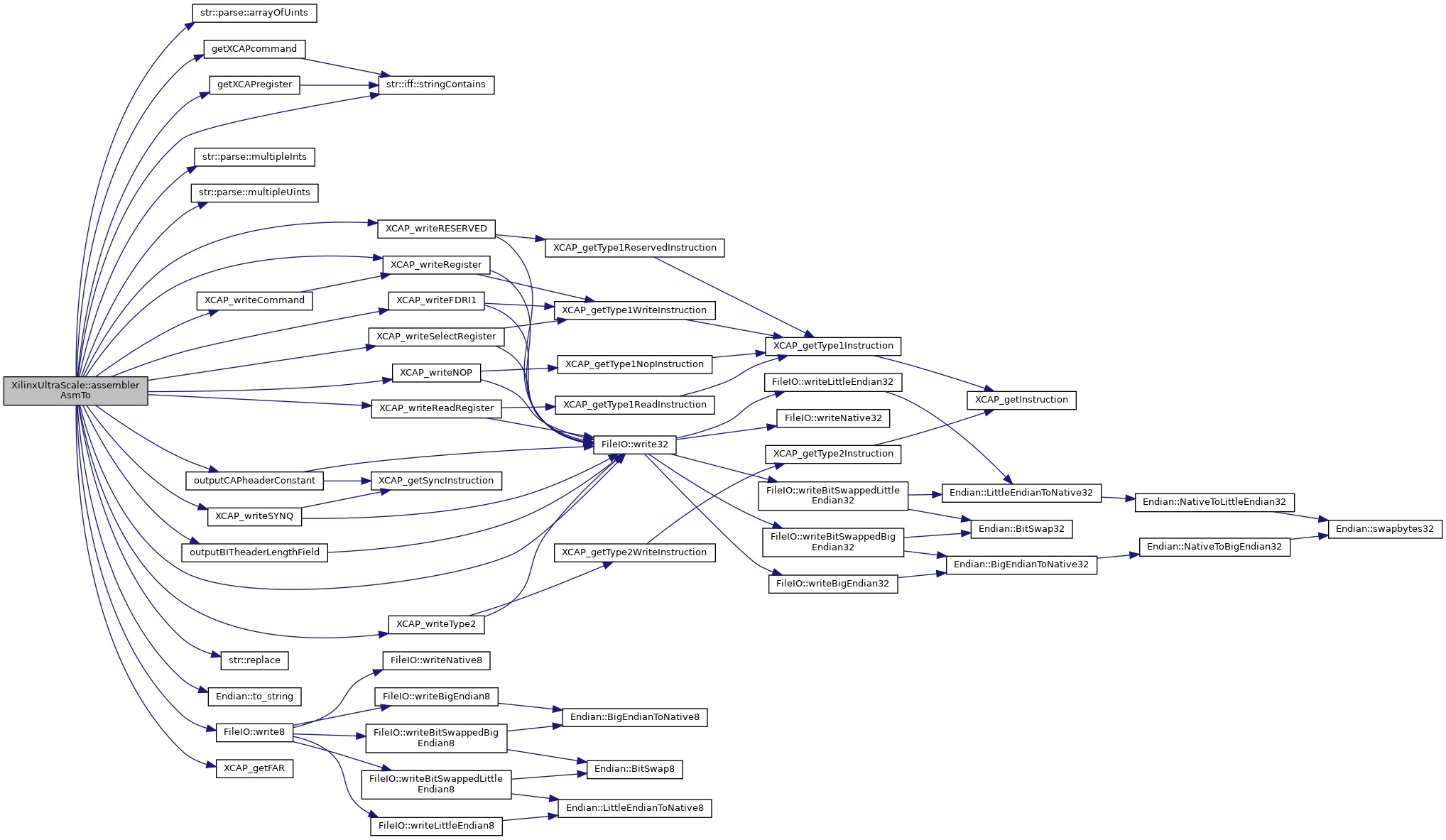

| void XilinxUltraScale::assemblerAsmTo | ( | std::ifstream & | , |

| std::ofstream & | |||

| ) |

Definition at line 125 of file XUS_Assembler.cpp.

References str::parse::arrayOfUints(), XCAP::FAR, XCAP::FDRI, getXCAPcommand(), getXCAPregister(), XCAP::MAGIC1, str::parse::multipleInts(), str::parse::multipleUints(), outputBITheaderLengthField(), outputCAPheaderConstant(), str::replace(), str::iff::stringContains(), Endian::to_string(), XCAP::UNDEFINED, FileIO::write32(), FileIO::write8(), XCAP_getFAR(), XCAP_writeCommand(), XCAP_writeFDRI1(), XCAP_writeNOP(), XCAP_writeReadRegister(), XCAP_writeRegister(), XCAP_writeRESERVED(), XCAP_writeSelectRegister(), XCAP_writeSYNQ(), XCAP_writeType2(), XUS_WORDS_AT_CLK, XUS_WORDS_BEFORE_CLK, and XUS_WORDS_PER_FRAME.

| void XilinxUltraScale::assemblerAsmToBin | ( | std::ifstream & | , |

| std::ofstream & | |||

| ) |

Definition at line 98 of file XUS_Assembler.cpp.

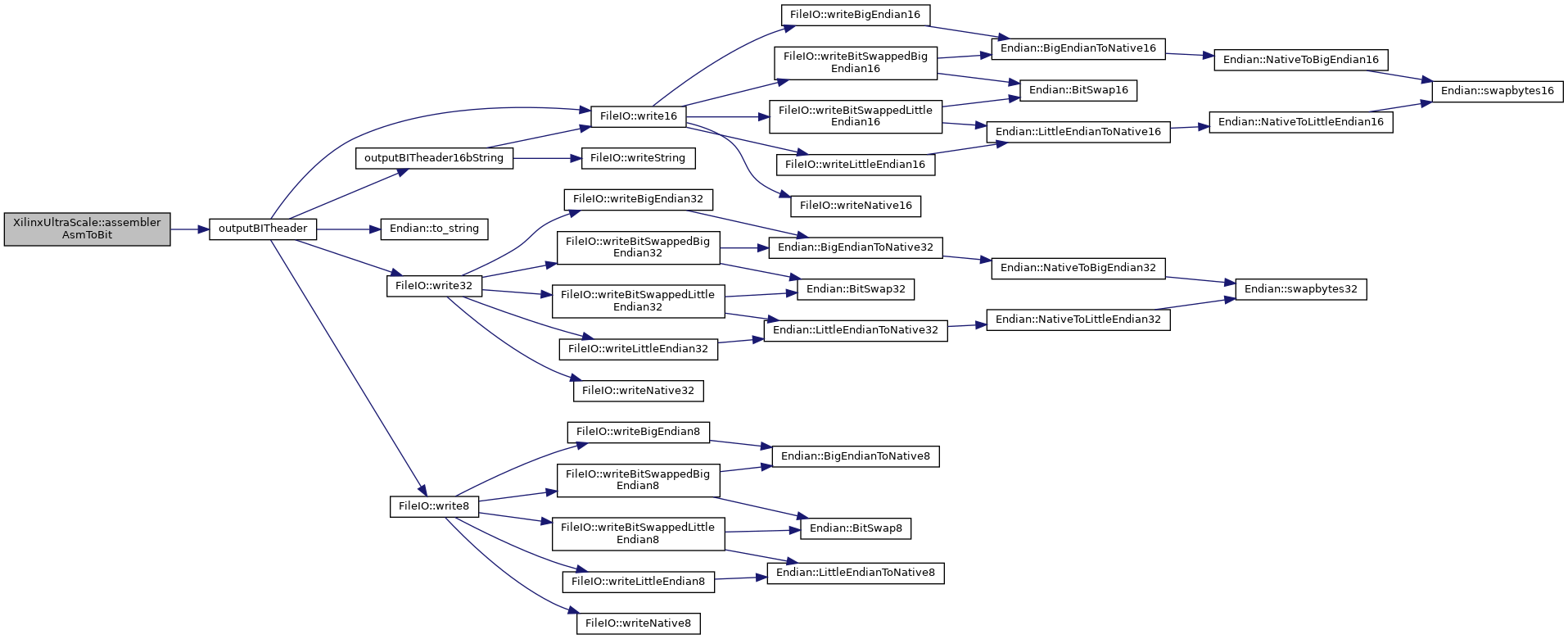

| void XilinxUltraScale::assemblerAsmToBit | ( | std::ifstream & | , |

| std::ofstream & | |||

| ) |

Definition at line 89 of file XUS_Assembler.cpp.

References outputBITheader().

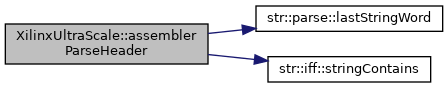

| void XilinxUltraScale::assemblerParseHeader | ( | std::ifstream & | ) |

Definition at line 107 of file XUS_Assembler.cpp.

References str::parse::lastStringWord(), and str::iff::stringContains().

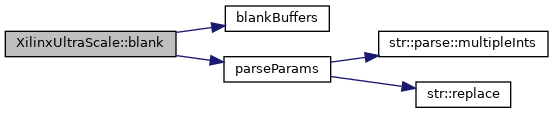

| void XilinxUltraScale::blank | ( | std::string | ) |

Definition at line 22 of file XUS_Blank.cpp.

References blankBuffers(), and parseParams().

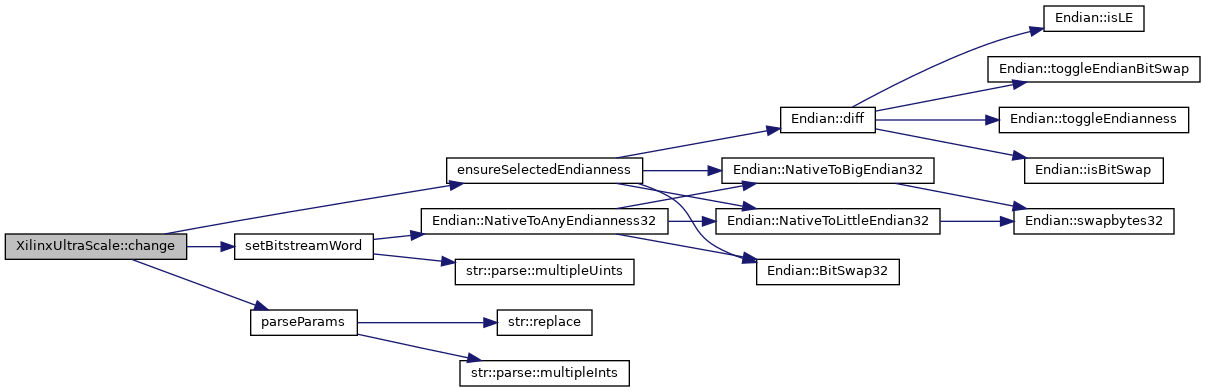

| void XilinxUltraScale::change | ( | std::string | ) |

Definition at line 25 of file XUS_Change.cpp.

References ensureSelectedEndianness(), parseParams(), and setBitstreamWord().

| void XilinxUltraScale::deviceHelp | ( | ) |

Definition at line 207 of file XUS_Devices.cpp.

References printResourceStringInfo().

| void XilinxUltraScale::disassemblerBinToAsm | ( | std::string | , |

| std::ifstream & | , | ||

| std::ofstream & | |||

| ) |

Definition at line 72 of file XUS_Assembler.cpp.

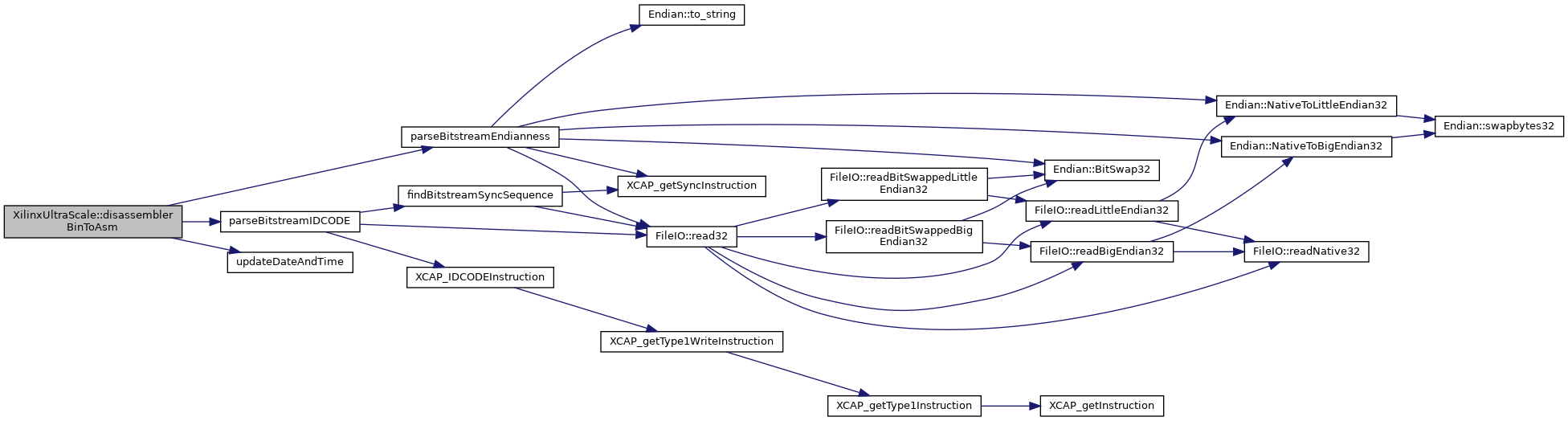

References parseBitstreamEndianness(), parseBitstreamIDCODE(), and updateDateAndTime().

| void XilinxUltraScale::disassemblerBitToAsm | ( | std::ifstream & | , |

| std::ofstream & | |||

| ) |

Definition at line 82 of file XUS_Assembler.cpp.

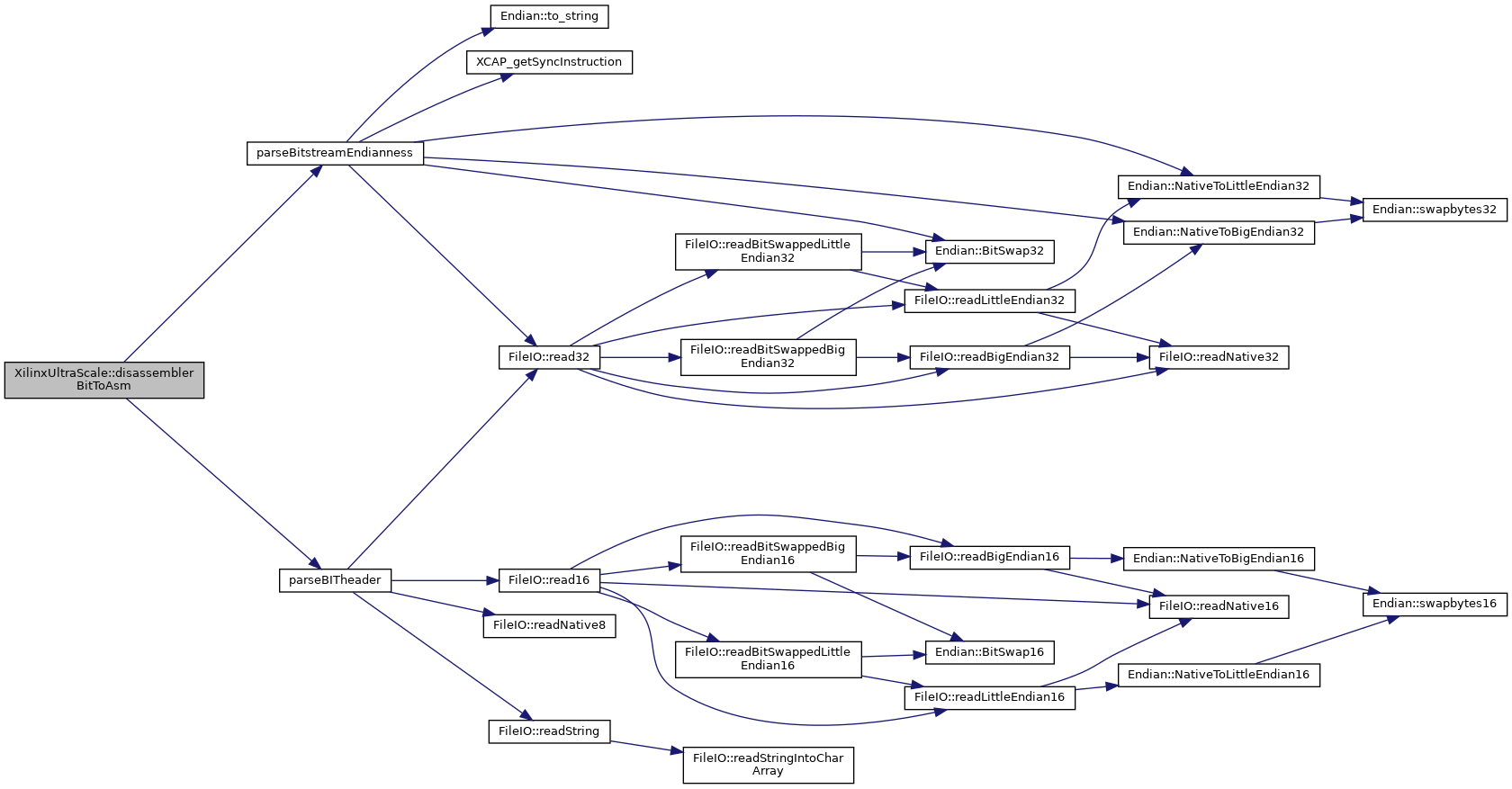

References parseBITheader(), and parseBitstreamEndianness().

| void XilinxUltraScale::disassemblerToAsm | ( | std::ifstream & | , |

| std::ofstream & | |||

| ) |

Definition at line 252 of file XUS_Assembler.cpp.

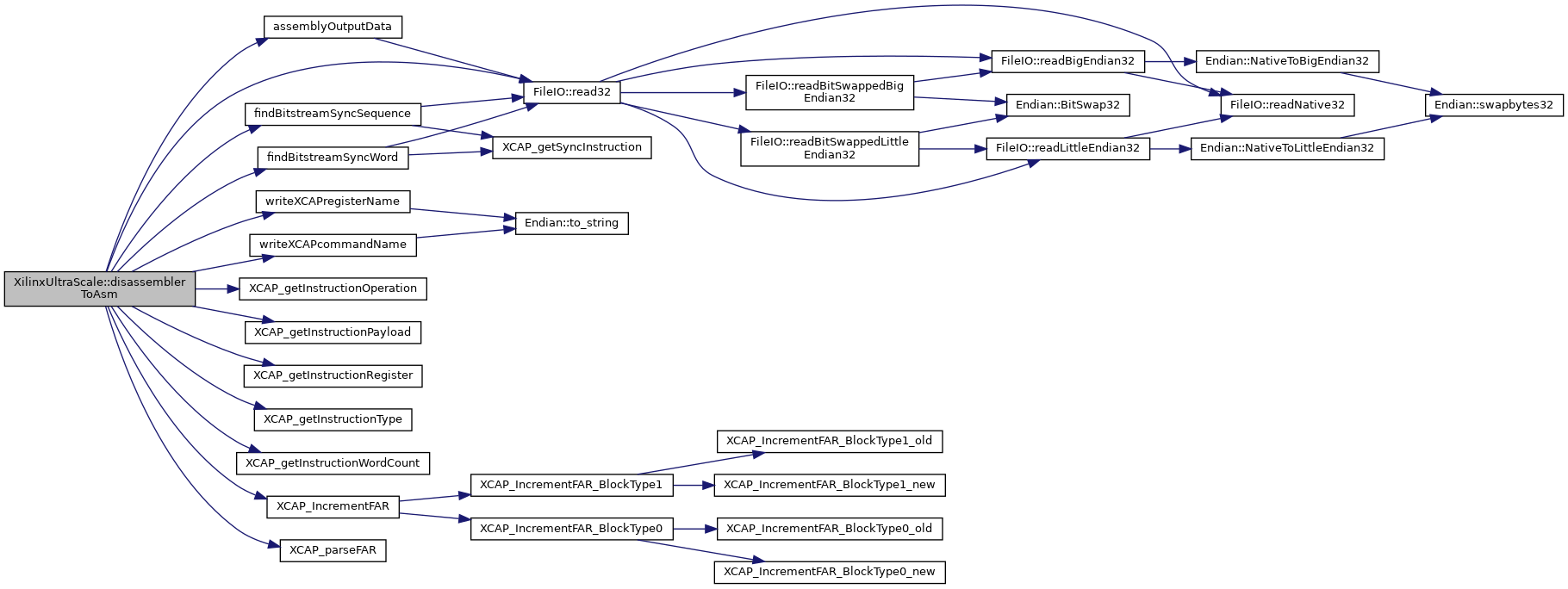

References assemblyOutputData(), XCAP::CMD, XCAP::DESYNC, XCAP::FAR, XCAP::FDRI, findBitstreamSyncSequence(), findBitstreamSyncWord(), XCAP::MAGIC1, XCAP::NOP, XCAP::READ, FileIO::read32(), XCAP::RESERVED, XCAP::UNDEFINED, XCAP::WCFG, XCAP::WRITE, writeXCAPcommandName(), writeXCAPregisterName(), XCAP_getInstructionOperation(), XCAP_getInstructionPayload(), XCAP_getInstructionRegister(), XCAP_getInstructionType(), XCAP_getInstructionWordCount(), XCAP_IncrementFAR(), XCAP_parseFAR(), XUS_WORDS_AT_CLK, XUS_WORDS_BEFORE_CLK, and XUS_WORDS_PER_FRAME.

| void XilinxUltraScale::disassemblerWriteHeader | ( | std::ofstream & | ) |

Definition at line 242 of file XUS_Assembler.cpp.

|

overridevirtual |

Definition at line 77 of file XilinxUltraScale.cpp.

References Endian::to_string(), XUS_EXTRA_FRAMES_PER_ROW, XUS_FRAMES_PER_BRAM_CONTENT_COLUMN, and XUS_WORDS_PER_FRAME.

|

overridevirtual |

Definition at line 58 of file XUS_Devices.cpp.

References XCKU025_IDCODE, XCKU035_IDCODE, XCKU040_IDCODE, XCKU060_IDCODE, XCKU085_IDCODE, XCKU095_IDCODE, XCKU115_IDCODE, XCVU065_IDCODE, XCVU080_IDCODE, XCVU095_IDCODE, XCVU125_IDCODE, XCVU160_IDCODE, XCVU190_IDCODE, XCVU440_IDCODE, XUS_DEVICE_NULL, XUS_DEVICE_XCKU025, XUS_DEVICE_XCKU035, XUS_DEVICE_XCKU040, XUS_DEVICE_XCKU060, XUS_DEVICE_XCKU085, XUS_DEVICE_XCKU095, XUS_DEVICE_XCKU115, XUS_DEVICE_XCVU065, XUS_DEVICE_XCVU080, XUS_DEVICE_XCVU095, XUS_DEVICE_XCVU125, XUS_DEVICE_XCVU160, XUS_DEVICE_XCVU190, and XUS_DEVICE_XCVU440.

|

overridevirtual |

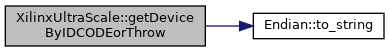

Definition at line 28 of file XUS_Devices.cpp.

References Endian::to_string(), and XUS_DEVICE_NULL.

|

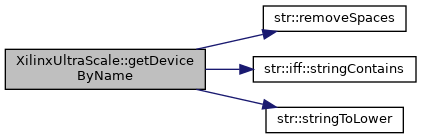

overridevirtual |

Definition at line 97 of file XUS_Devices.cpp.

References str::removeSpaces(), str::iff::stringContains(), str::stringToLower(), XCKU025_NAME, XCKU035_NAME, XCKU040_NAME, XCKU060_NAME, XCKU085_NAME, XCKU095_NAME, XCKU115_NAME, XCVU065_NAME, XCVU080_NAME, XCVU095_NAME, XCVU125_NAME, XCVU160_NAME, XCVU190_NAME, XCVU440_NAME, XUS_DEVICE_NULL, XUS_DEVICE_XCKU025, XUS_DEVICE_XCKU035, XUS_DEVICE_XCKU040, XUS_DEVICE_XCKU060, XUS_DEVICE_XCKU085, XUS_DEVICE_XCKU095, XUS_DEVICE_XCKU115, XUS_DEVICE_XCVU065, XUS_DEVICE_XCVU080, XUS_DEVICE_XCVU095, XUS_DEVICE_XCVU125, XUS_DEVICE_XCVU160, XUS_DEVICE_XCVU190, and XUS_DEVICE_XCVU440.

|

overridevirtual |

Definition at line 36 of file XUS_Devices.cpp.

References XUS_DEVICE_NULL.

|

overridevirtual |

Definition at line 116 of file XilinxUltraScale.cpp.

References XUS_BLOCKTYPE_BLOCKRAM, and XUS_BLOCKTYPE_LOGIC.

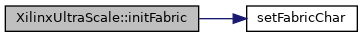

| void XilinxUltraScale::initFabric | ( | ) |

Definition at line 22 of file XUS_Fabric.cpp.

References setFabricChar(), and XUS_EXTRA_FRAMES_PER_ROW.

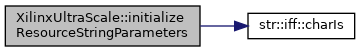

|

overridevirtual |

Definition at line 40 of file XilinxUltraScale.cpp.

References str::iff::charIs(), XUS_MAX_COLS, and XUS_WORDS_PER_FRAME.

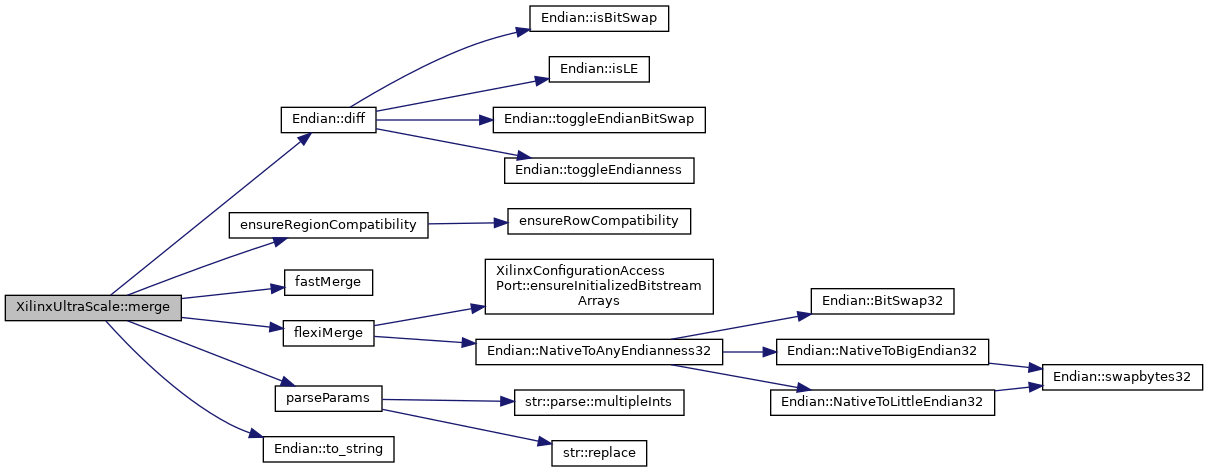

| void XilinxUltraScale::merge | ( | XilinxUltraScale * | , |

| std::string | , | ||

| Rect2D | , | ||

| Coord2D | |||

| ) |

Definition at line 24 of file XUS_Merge.cpp.

References Coord2D::col, Endian::diff(), ensureRegionCompatibility(), fastMerge(), flexiMerge(), XilinxConfigurationAccessPort< MAX_SLRS, MAX_ROWS, MAX_COLS, MAX_BRAM_COLS, BLOCKTYPE_MAX, BLOCKTYPE_LOGIC, BLOCKTYPE_BLOCKRAM, WORDS_BEFORE_CLK, WORDS_AT_CLK, WORDS_AFTER_CLK, WORDS_PER_FRAME, FRAMES_PER_BRAM_CONTENT_COLUMN, CLB_PER_CLOCK_REGION, BRAM_PER_CLOCK_REGION, EXTRA_FRAMES_PER_ROW, FAR_ENABLE_TOP_BOTTOM_BIT, FAR_TOP_BOTTOM_BIT_SHIFT, FAR_BLOCKTYPE_SHIFT, FAR_BLOCKTYPE_MASK, FAR_ROWADDRESS_SHIFT, FAR_ROWADDRESS_MASK, FAR_COLUMNADDRESS_SHIFT, FAR_COLUMNADDRESS_MASK, FAR_MINORADDRESS_SHIFT, FAR_MINORADDRESS_MASK >::loadedBitstreamEndianness, NATIVE, parseParams(), Rect2D::position, Coord2D::row, Rect2D::size, Endian::to_string(), and XUS_CLB_PER_CLOCK_REGION.

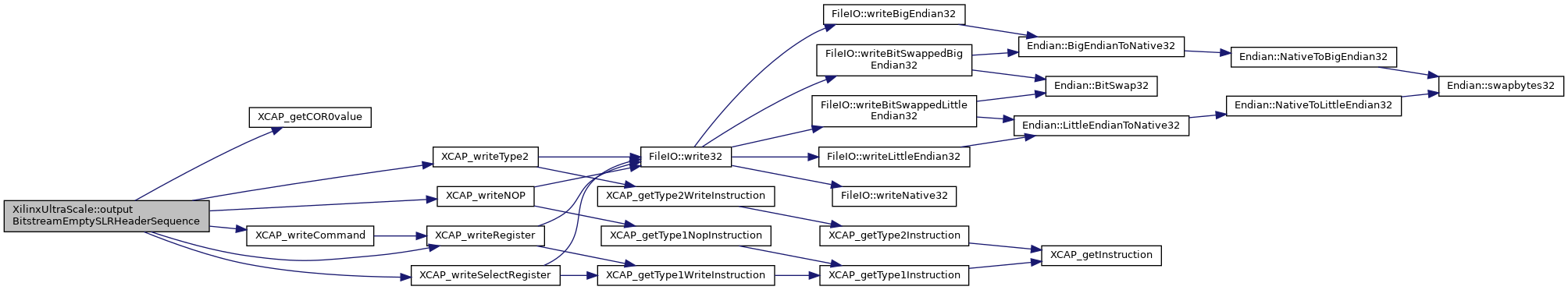

|

overridevirtual |

Definition at line 121 of file XUS_Output.cpp.

References XCAP::COR0, XCAP::IDCODE, XCAP::MAGIC1, NoWait, XCAP::NULLCMD, Phase4, Phase5, Phase6, XCAP::RCRC, XCAP_getCOR0value(), XCAP_writeCommand(), XCAP_writeNOP(), XCAP_writeRegister(), XCAP_writeSelectRegister(), and XCAP_writeType2().

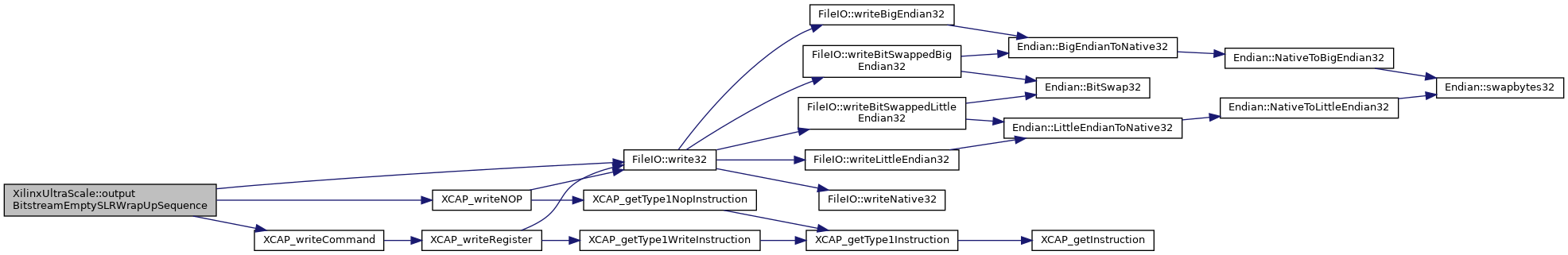

|

overridevirtual |

Definition at line 139 of file XUS_Output.cpp.

References XCAP::DESYNC, XCAP::START, FileIO::write32(), XCAP_writeCommand(), and XCAP_writeNOP().

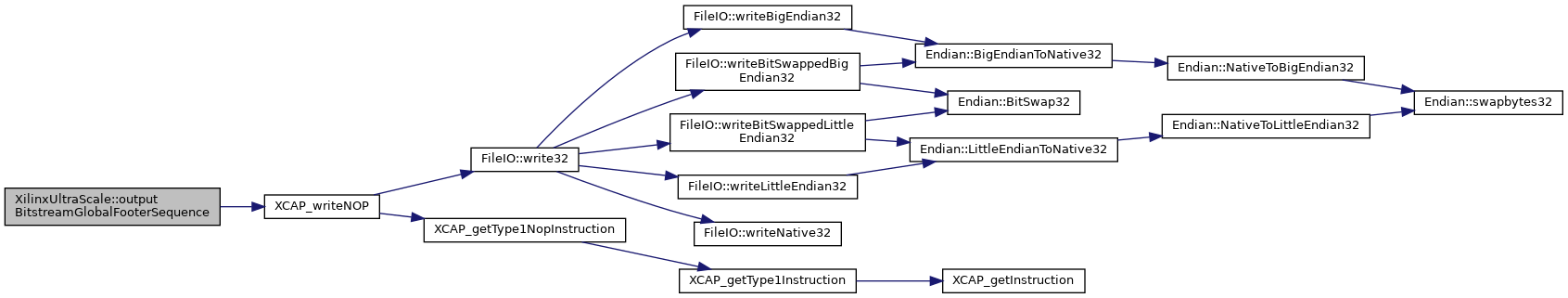

|

overridevirtual |

Definition at line 34 of file XUS_Output.cpp.

References XCAP_writeNOP().

|

overridevirtual |

Written by outputBitstreamSLRHeaderAfterBitstreamSequence(), outputBitstreamEmptySLRHeaderSequence() and used by outputBitstreamSLRWrapUpSequence(), outputBitstreamEmptySLRWrapUpSequence()

Definition at line 29 of file XUS_Output.cpp.

|

overridevirtual |

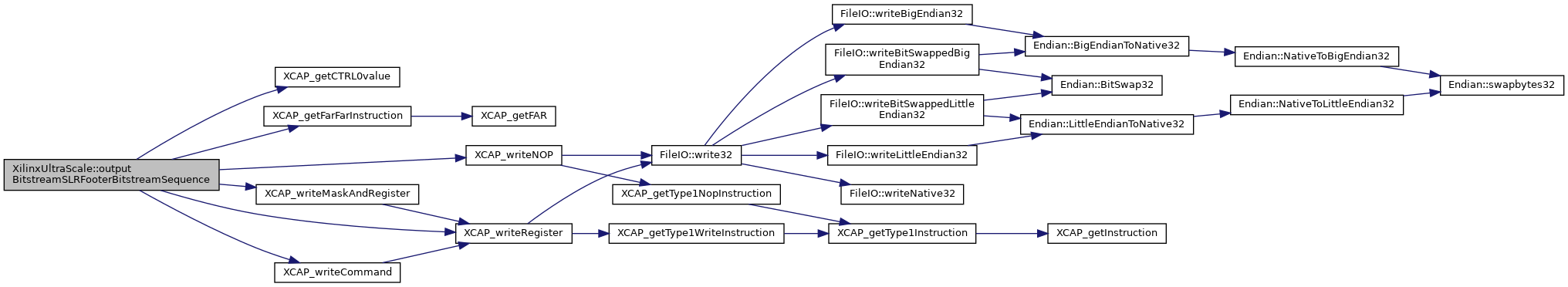

Definition at line 62 of file XUS_Output.cpp.

References XCAP::CTRL0, XCAP::DESYNC, XCAP::DGHIGH, XCAP::FAR, XCAP::GRESTORE, XCAP::MAGIC2, XCAP::RCRC, XCAP::START, XCAP_getCTRL0value(), XCAP_getFarFarInstruction(), XCAP_writeCommand(), XCAP_writeMaskAndRegister(), XCAP_writeNOP(), and XCAP_writeRegister().

|

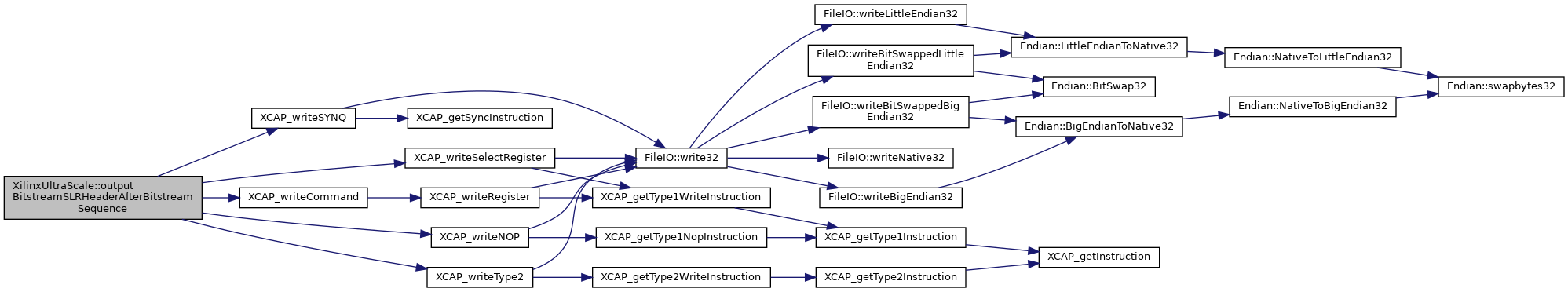

overridevirtual |

Definition at line 91 of file XUS_Output.cpp.

References XCAP::MAGIC1, XCAP::RCRC, XCAP_writeCommand(), XCAP_writeNOP(), XCAP_writeSelectRegister(), XCAP_writeSYNQ(), and XCAP_writeType2().

|

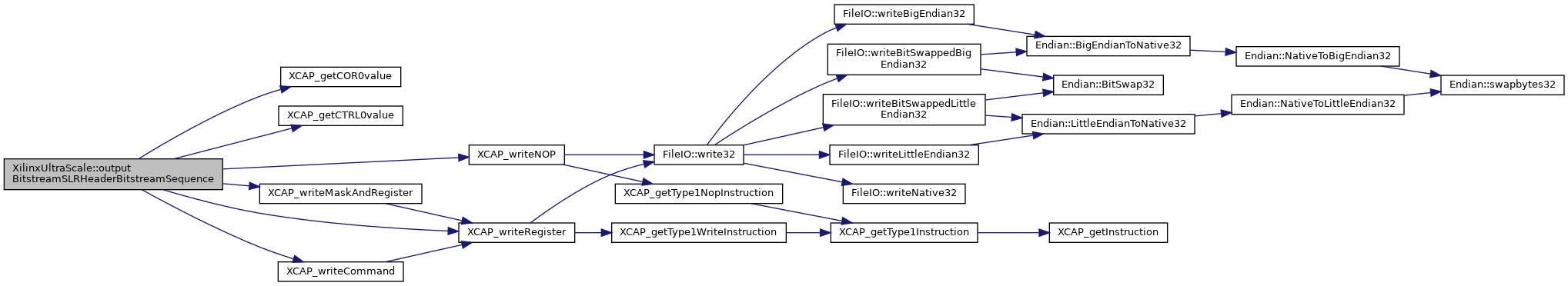

overridevirtual |

Definition at line 39 of file XUS_Output.cpp.

References XCAP::AGHIGH, XCAP::COR0, XCAP::CTRL0, XCAP::IDCODE, NoWait, XCAP::NULLCMD, Phase4, Phase5, Phase6, XCAP::RCRC, XCAP_getCOR0value(), XCAP_getCTRL0value(), XCAP_writeCommand(), XCAP_writeMaskAndRegister(), XCAP_writeNOP(), and XCAP_writeRegister().

|

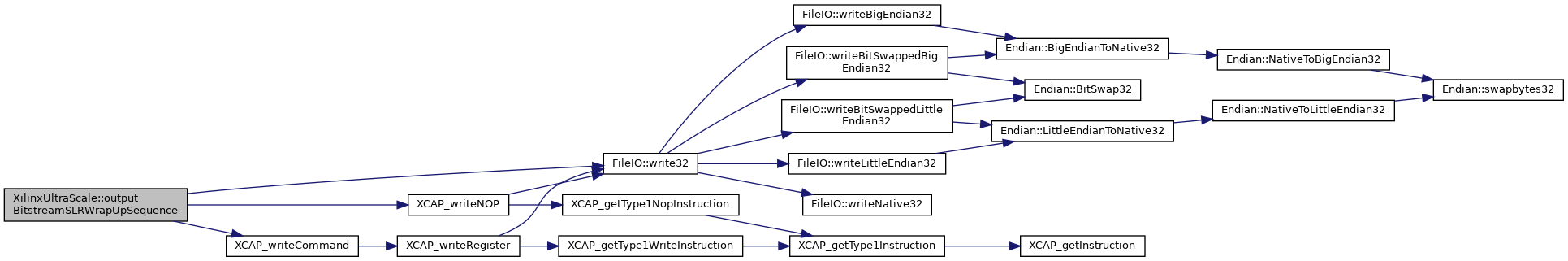

overridevirtual |

Definition at line 107 of file XUS_Output.cpp.

References XCAP::DESYNC, XCAP::START, FileIO::write32(), XCAP_writeCommand(), and XCAP_writeNOP().

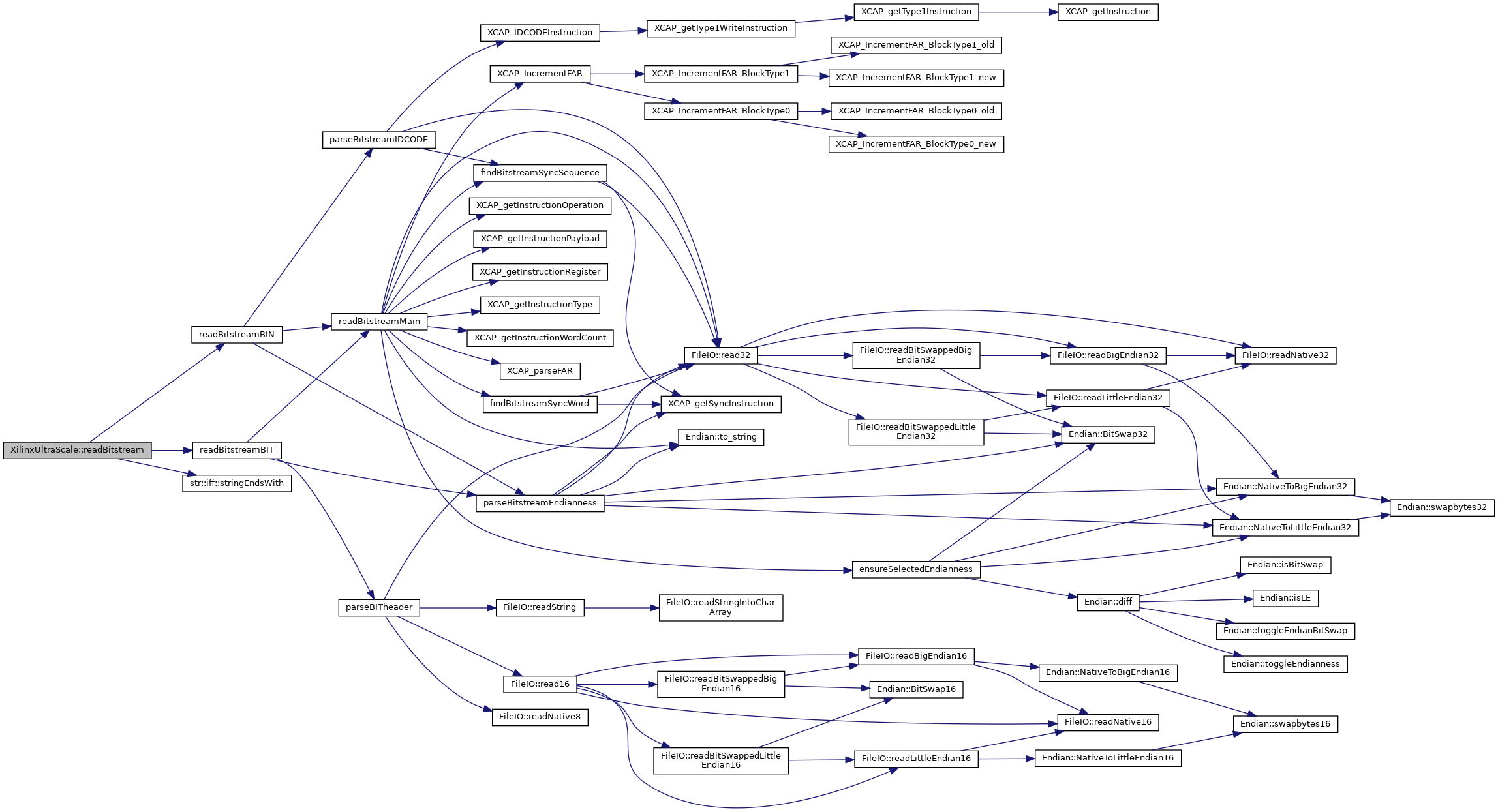

| void XilinxUltraScale::readBitstream | ( | std::string | ) |

Definition at line 29 of file XUS_Input.cpp.

References readBitstreamBIN(), readBitstreamBIT(), and str::iff::stringEndsWith().

|

overridevirtual |

Definition at line 142 of file XUS_Devices.cpp.

References clearResourceStringArrays(), XCKU025, XCKU035, XCKU040, XCKU060, XCKU085, XCKU095, XCKU115, XCVU065, XCVU080, XCVU095, XCVU125, XCVU160, XCVU190, XCVU440, XUS_DEVICE_XCKU025, XUS_DEVICE_XCKU035, XUS_DEVICE_XCKU040, XUS_DEVICE_XCKU060, XUS_DEVICE_XCKU085, XUS_DEVICE_XCKU095, XUS_DEVICE_XCKU115, XUS_DEVICE_XCVU065, XUS_DEVICE_XCVU080, XUS_DEVICE_XCVU095, XUS_DEVICE_XCVU125, XUS_DEVICE_XCVU160, XUS_DEVICE_XCVU190, and XUS_DEVICE_XCVU440.

|

overridevirtual |

Definition at line 53 of file XUS_Devices.cpp.

|

overridevirtual |

Definition at line 48 of file XUS_Devices.cpp.

|

overridevirtual |

Definition at line 44 of file XUS_Devices.cpp.

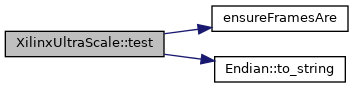

| void XilinxUltraScale::test | ( | bool | usableFramesOnly, |

| bool | testValueEqual, | ||

| uint32_t | testValue | ||

| ) |

Definition at line 23 of file XUS_Test.cpp.

References ensureFramesAre(), and Endian::to_string().

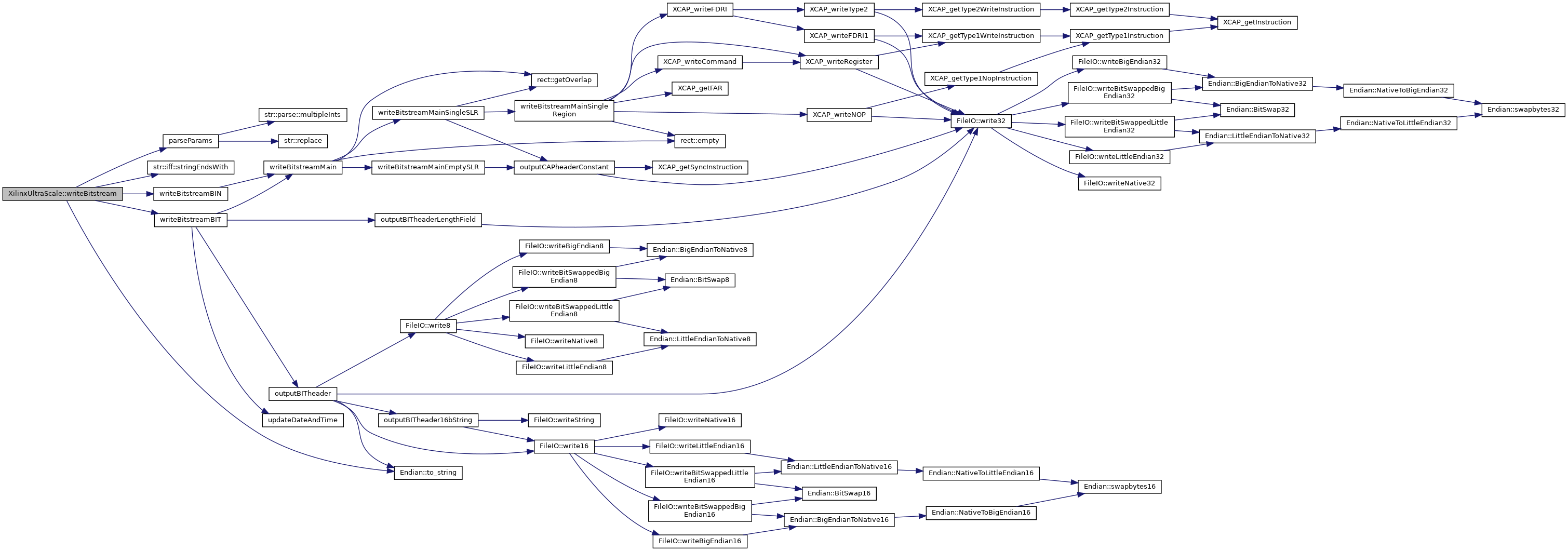

| void XilinxUltraScale::writeBitstream | ( | std::string | , |

| std::string | , | ||

| Rect2D | |||

| ) |

Creates a new bitstream file and writes the selected regions in it.

filename Name of the output file. | runtime_error | if args don't define a correct region. |

Definition at line 160 of file XUS_Output.cpp.

References Coord2D::col, parseParams(), Rect2D::position, Coord2D::row, Rect2D::size, str::iff::stringEndsWith(), Endian::to_string(), writeBitstreamBIN(), writeBitstreamBIT(), and XUS_CLB_PER_CLOCK_REGION.

| std::streamoff XilinxUltraScale::slrMagicInstrLocation[3] |

Definition at line 51 of file XilinxUltraScale.h.