|

byteman

1.3 (Build #225)

Bitstream relocation and manipulation tool

|

|

byteman

1.3 (Build #225)

Bitstream relocation and manipulation tool

|

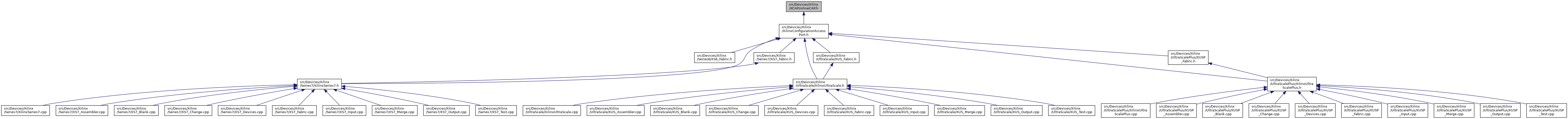

Go to the source code of this file.

Macros | |

| #define | FABRIC_SYNC_WORD 0xAA995566 |

Enumerations | |

| enum class | DONE_CYCLE { Phase1 = 0 , Phase2 = 1 , Phase3 = 2 , Phase4 = 3 , Phase5 = 4 , Phase6 = 5 } |

| enum class | GTS_CYCLE { Phase1 = 0 , Phase2 = 1 , Phase3 = 2 , Phase4 = 3 , Phase5 = 4 , Phase6 = 5 , GTS_DONE = 6 } |

| enum class | GWE_CYCLE { Phase1 = 0 , Phase2 = 1 , Phase3 = 2 , Phase4 = 3 , Phase5 = 4 , Phase6 = 5 , GWE_DONE = 6 } |

| enum class | LOCK_CYCLE { Phase0 = 0 , Phase1 = 1 , Phase2 = 2 , Phase3 = 3 , Phase4 = 4 , Phase5 = 5 , Phase6 = 6 , NoWait = 7 } |

| enum class | MATCH_CYCLE { Phase0 = 0 , Phase1 = 1 , Phase2 = 2 , Phase3 = 3 , Phase4 = 4 , Phase5 = 5 , Phase6 = 6 , NoWait = 7 } |

Functions | |

| XCAP::Command | getXCAPcommand (std::string s) |

| XCAP::Register | getXCAPregister (std::string s) |

| void | writeXCAPcommandName (std::ofstream &fout, XCAP::Command commandID) |

| void | writeXCAPregisterName (std::ofstream &fout, XCAP::Register registerID) |

| uint32_t | XCAP_getCOR0value (int Reserved_31_27, int ECLK_EN, int Reserved_25, int DRIVE_DONE, int Reserved_23, int OSCFSEL, int Reserved_16_15, DONE_CYCLE selDONE_CYCLE, MATCH_CYCLE selMATCH_CYCLE, LOCK_CYCLE selLOCK_CYCLE, GTS_CYCLE selGTS_CYCLE, GWE_CYCLE selGWE_CYCLE) |

| Generate COR0 register write value. More... | |

| uint32_t | XCAP_getCTRL0value (int EFUSE_KEY, int ICAP_SELECT, int Reserved_29_13, int OverTempShutDown, int Reserved_11, int ConfigFallback, int Reserved_9, int GLUTMASK_B, int Reserved_7, int DEC, int SBITS, int PERSIST, int Reserved_2_1, int GTS_USR_B) |

| Generate CTRL0 register write value. More... | |

| uint32_t | XCAP_getInstruction (int type, XCAP::Operation operation, XCAP::Register reg, int payload) |

| Generate and return the encoding for an instruction. More... | |

| XCAP::Operation | XCAP_getInstructionOperation (uint32_t instruction) |

| Parses and returns instruction operation. Most Xil instructions will NOP or write. More... | |

| uint32_t | XCAP_getInstructionPayload (uint32_t instruction) |

| Parses and returns instruction payload. This is the immediate value after instruction type and operation encodings. More... | |

| XCAP::Register | XCAP_getInstructionRegister (uint32_t instruction) |

| Parses and returns instruction register. This is the register being addressed if the instruction is of type 1. More... | |

| uint32_t | XCAP_getInstructionType (uint32_t instruction) |

| Parses and returns instruction type. Valid Xil instructions will be of types 1 and 2. More... | |

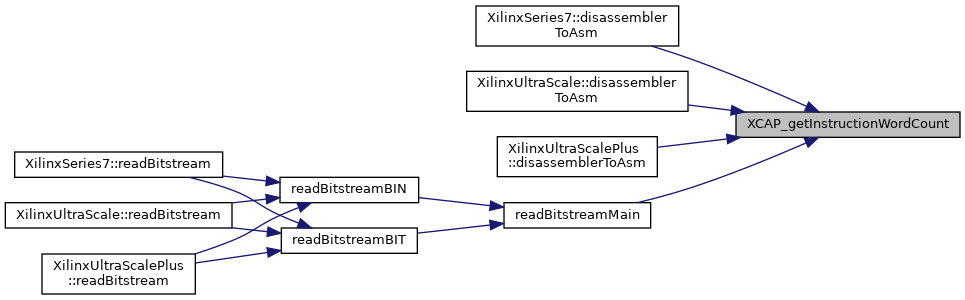

| uint32_t | XCAP_getInstructionWordCount (uint32_t instruction) |

| Parses and returns instruction word count. This is the number of words to be read/written if the instruction is of type 1. More... | |

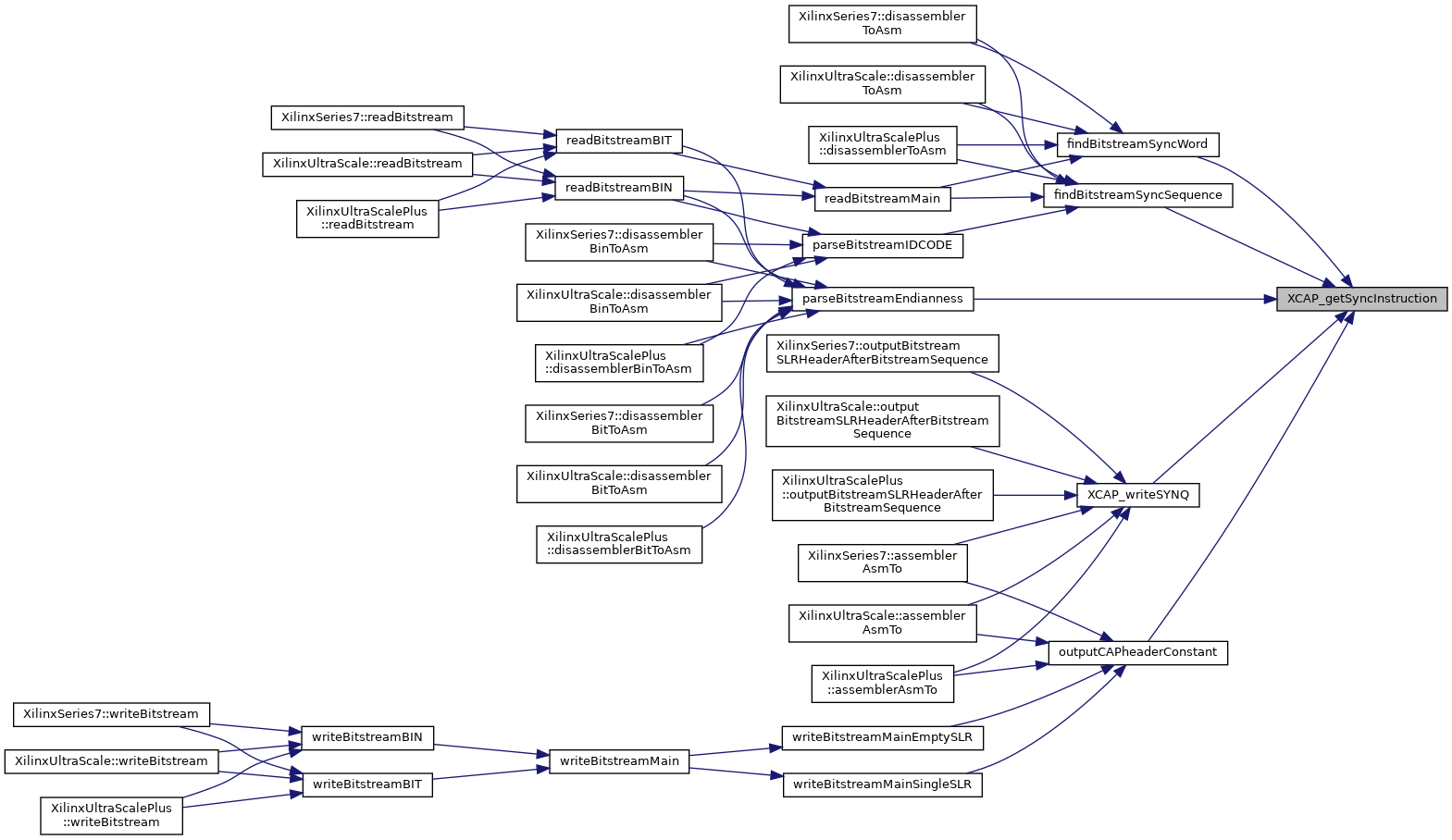

| uint32_t | XCAP_getSyncInstruction () |

| Generate and return the encoding for a SYNC instruction. More... | |

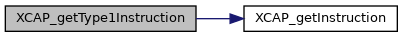

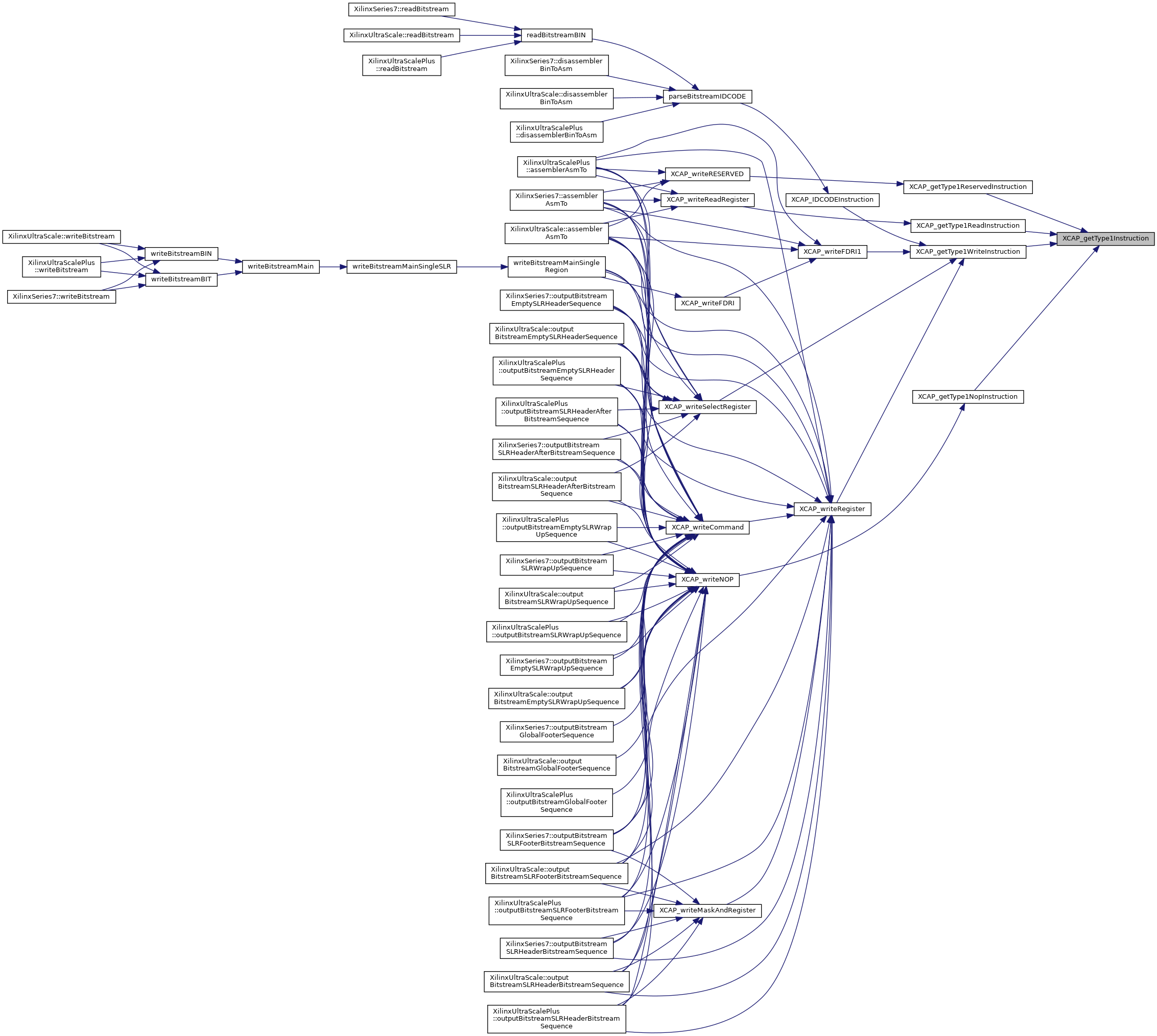

| uint32_t | XCAP_getType1Instruction (XCAP::Operation operation, XCAP::Register reg, int payload) |

| Generate and return the encoding for a type 1 instruction. More... | |

| uint32_t | XCAP_getType1NopInstruction (int payload) |

| Generate and return the encoding for a type 1 NOP instruction. More... | |

| uint32_t | XCAP_getType1ReadInstruction (XCAP::Register reg, int payload) |

| Generate and return the encoding for a type 1 Read instruction. More... | |

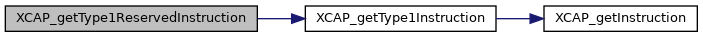

| uint32_t | XCAP_getType1ReservedInstruction (int payload) |

| Generate and return the encoding for a type 1 Reserved instruction. More... | |

| uint32_t | XCAP_getType1WriteInstruction (XCAP::Register reg, int payload) |

| Generate and return the encoding for a type 1 Write instruction. More... | |

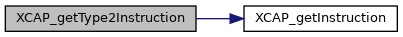

| uint32_t | XCAP_getType2Instruction (XCAP::Operation operation, int payload) |

| Generate and return the encoding for a type 2 instruction. More... | |

| uint32_t | XCAP_getType2NopInstruction (int payload) |

| Generate and return the encoding for a type 2 NOP instruction. More... | |

| uint32_t | XCAP_getType2ReadInstruction (int payload) |

| Generate and return the encoding for a type 2 Read instruction. More... | |

| uint32_t | XCAP_getType2ReservedInstruction (int payload) |

| Generate and return the encoding for a type 2 Reserved instruction. More... | |

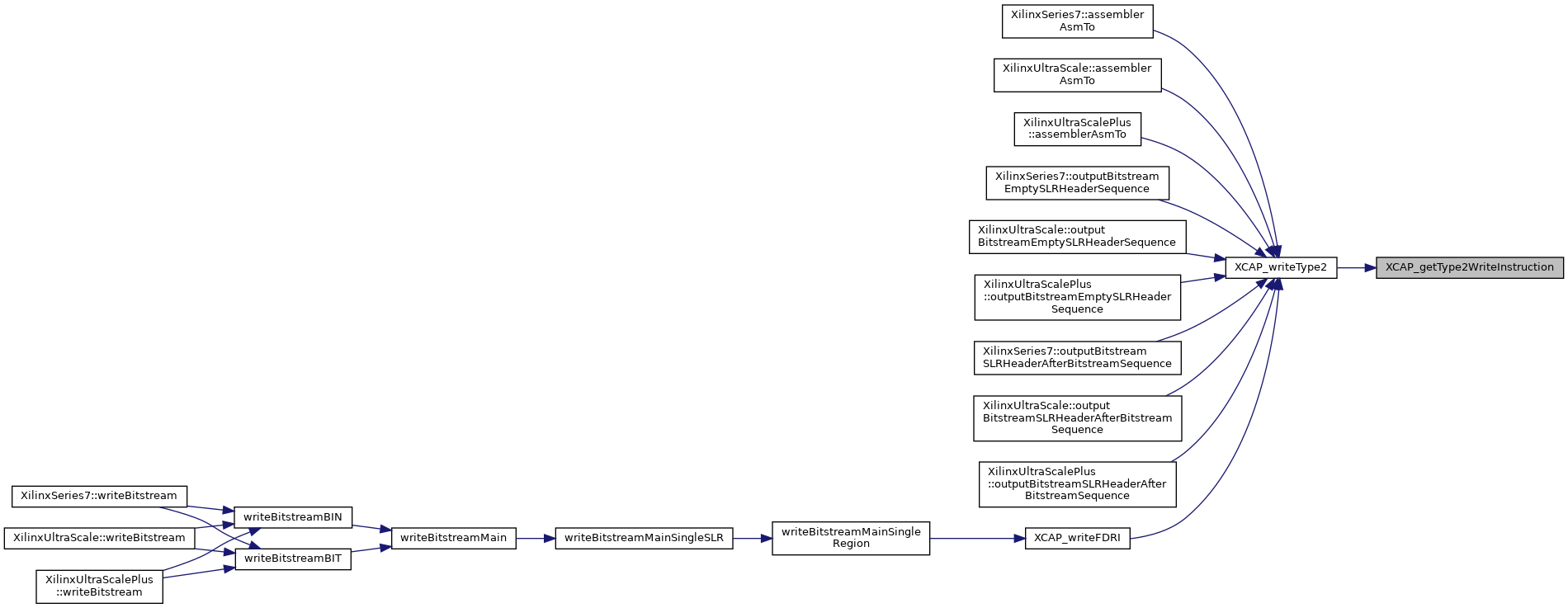

| uint32_t | XCAP_getType2WriteInstruction (int payload) |

| Generate and return the encoding for a type 2 Write instruction. More... | |

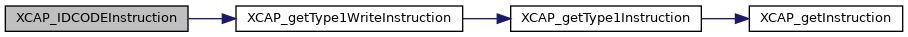

| uint32_t | XCAP_IDCODEInstruction () |

| Generate and return the encoding for a IDCODE writing instruction. More... | |

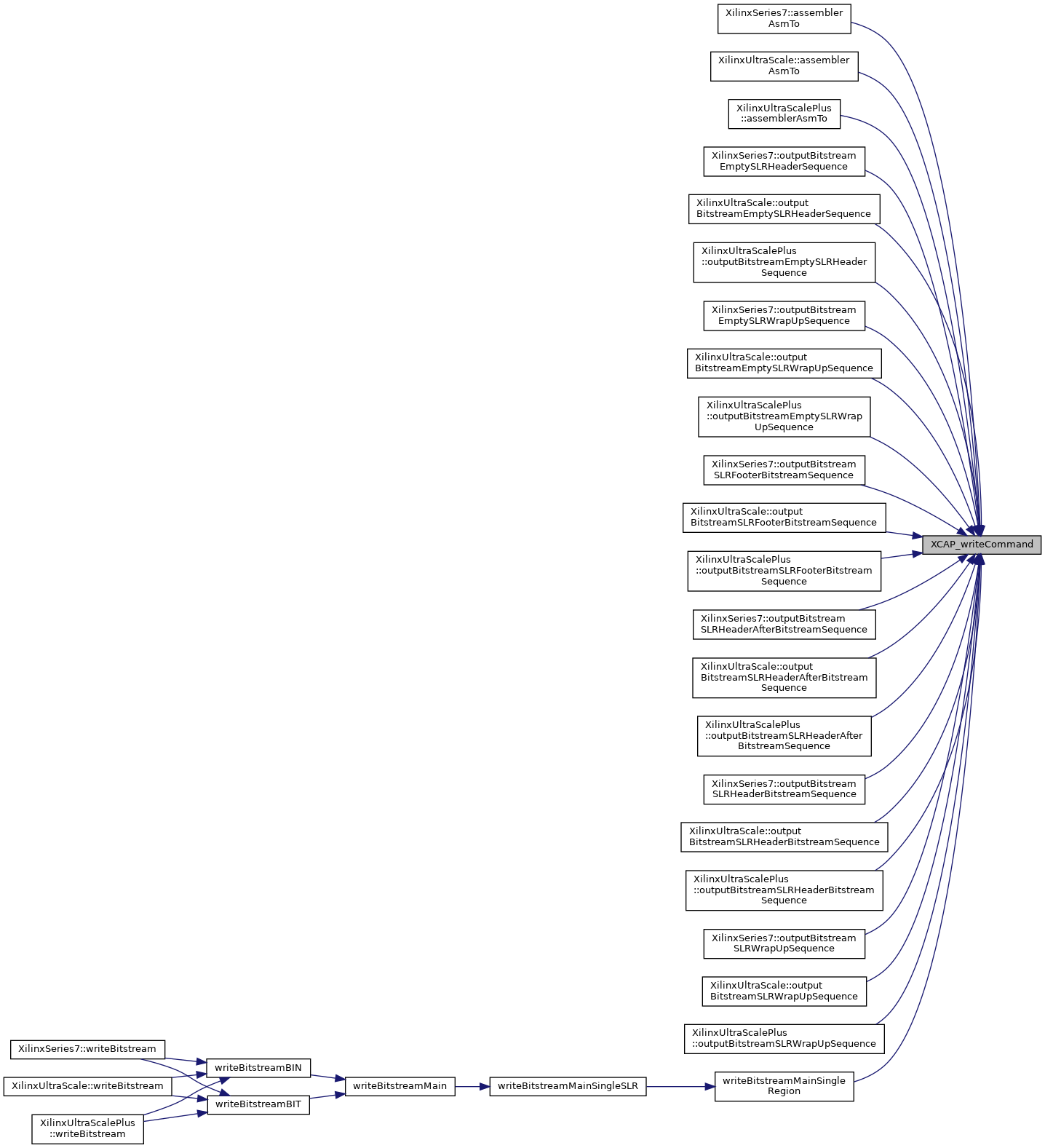

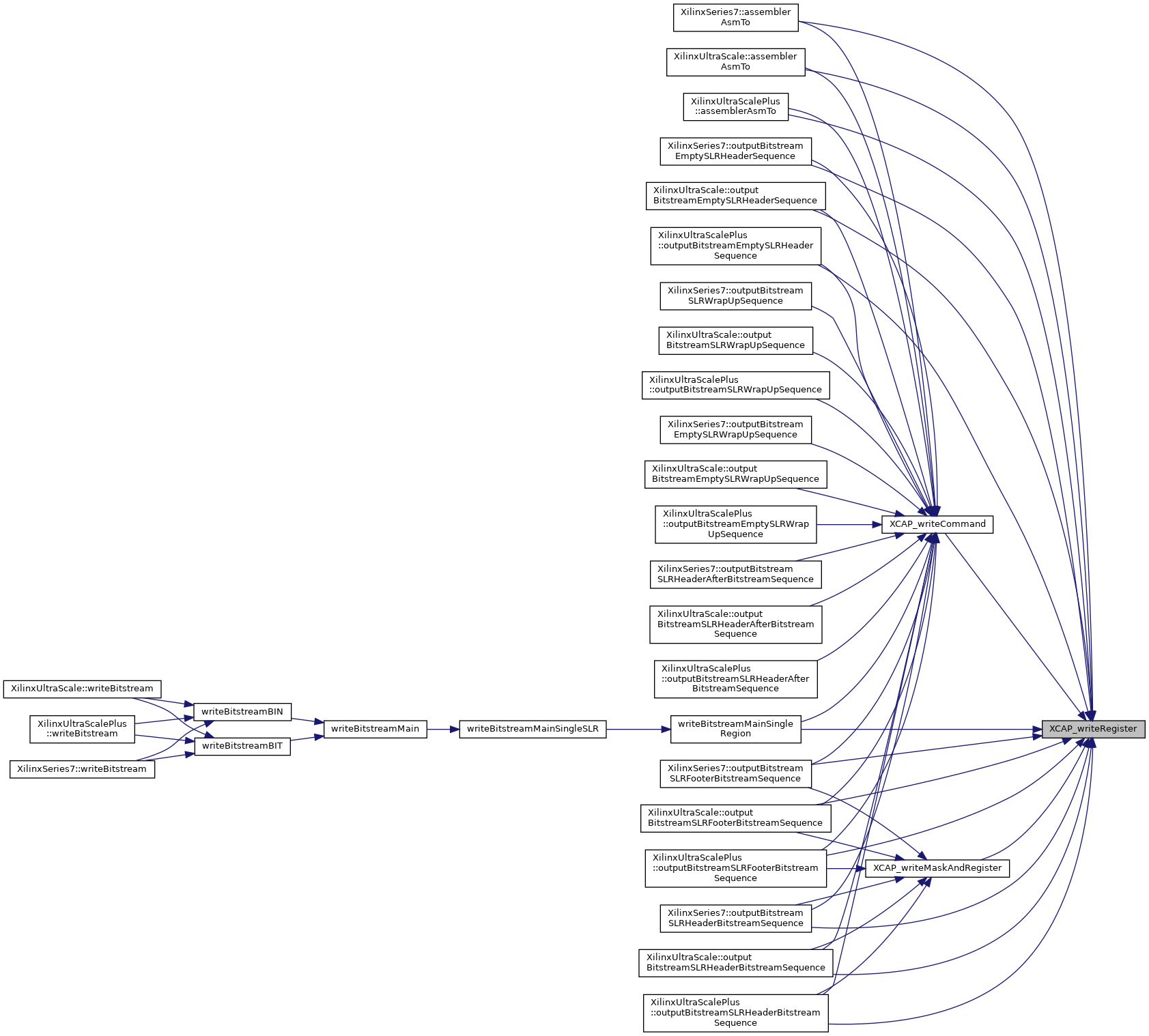

| void | XCAP_writeCommand (std::ofstream &fout, XCAP::Command cmd, Endianness e) |

| Generate the encoding for writing a CAP command and write it to file ofstream. More... | |

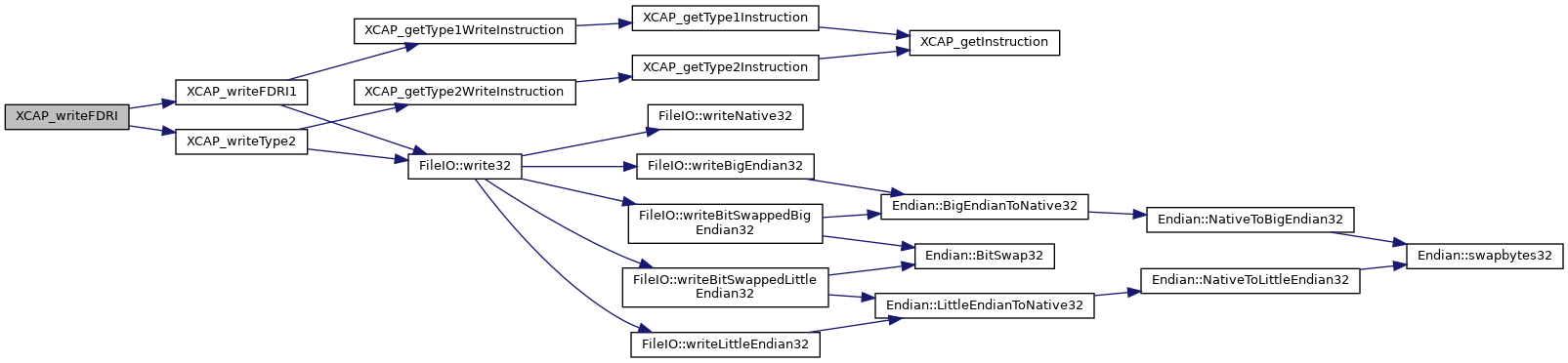

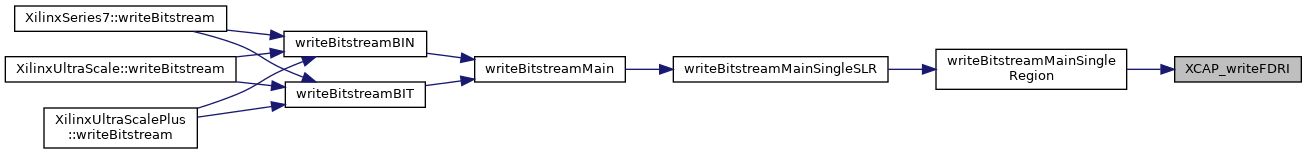

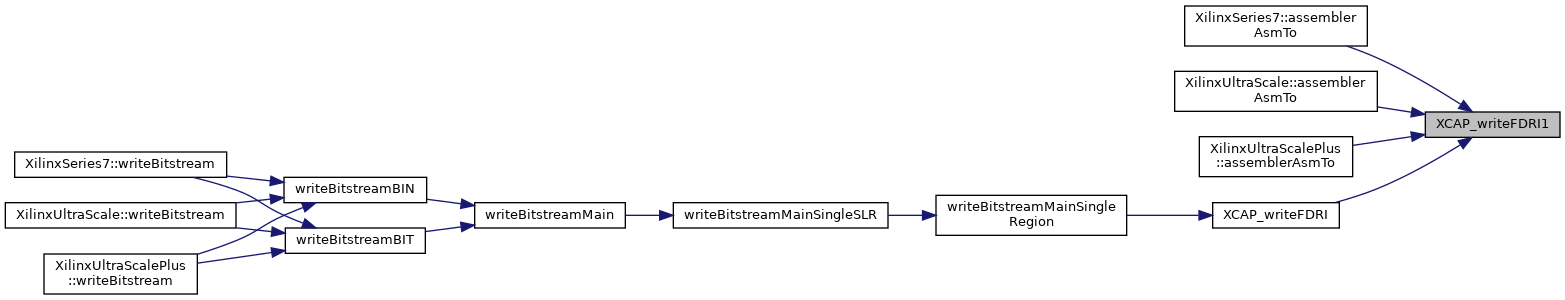

| void | XCAP_writeFDRI (std::ofstream &fout, int wordCount, Endianness e) |

| Generate and write an FDRI command. Always uses type 2 command for simplicity. More... | |

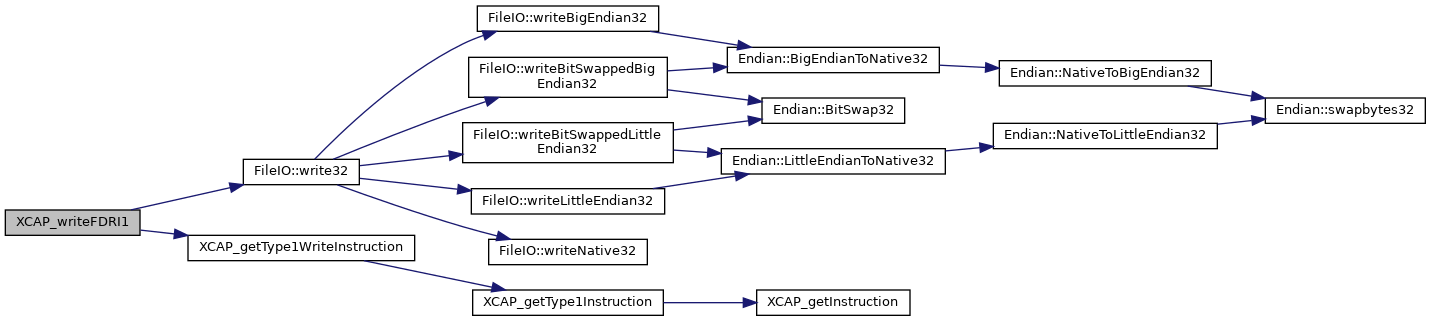

| void | XCAP_writeFDRI1 (std::ofstream &fout, int wordCount, Endianness e) |

| Generate and write only a type 1 FDRI command. More... | |

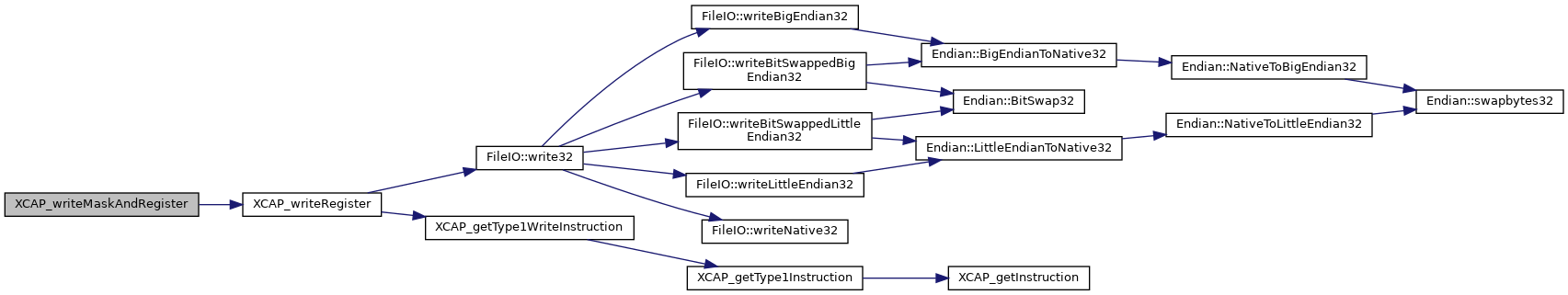

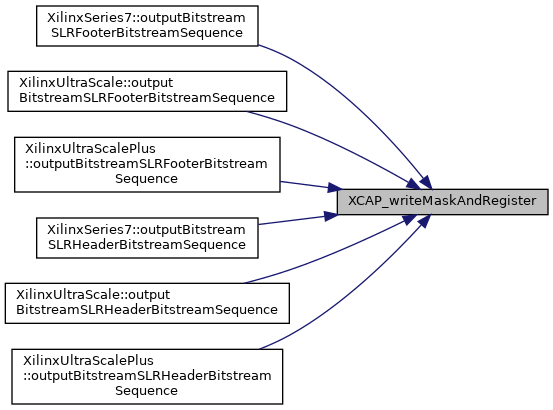

| void | XCAP_writeMaskAndRegister (std::ofstream &fout, XCAP::Register reg, int writeMask, int writeValue, Endianness e) |

| Generate the encoding for writing a CAP register with a mask and write it to file ofstream. More... | |

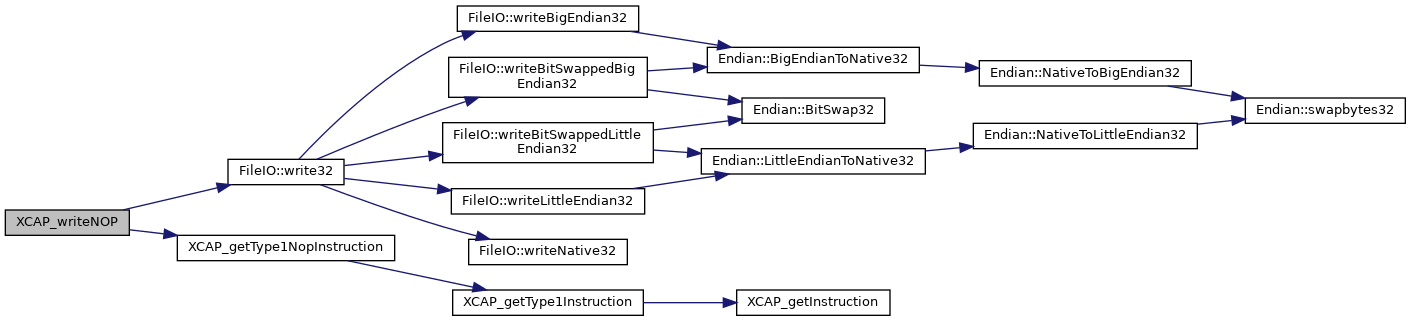

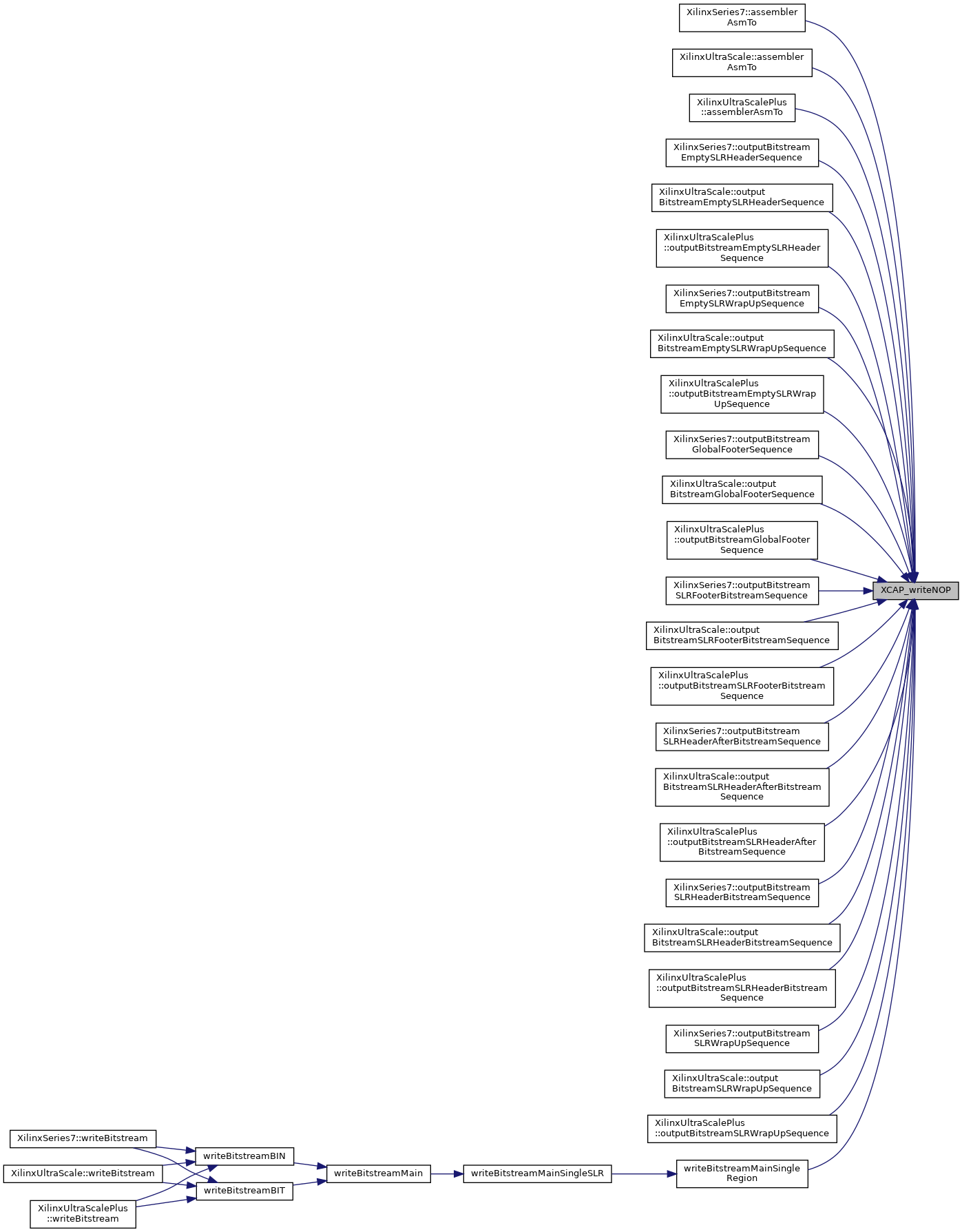

| void | XCAP_writeNOP (std::ofstream &fout, int cnt, int payload, Endianness e) |

| Generate the encoding for NOP instructions and write them to file ofstream. More... | |

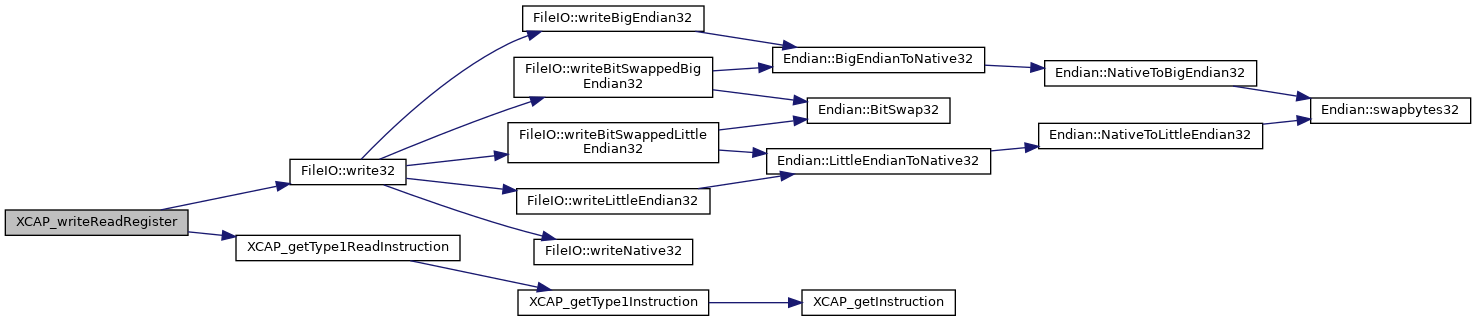

| void | XCAP_writeReadRegister (std::ofstream &fout, XCAP::Register reg, int readLength, Endianness e) |

| Generate the encoding for reading a CAP register and write it to file ofstream. More... | |

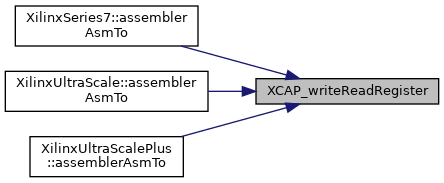

| void | XCAP_writeRegister (std::ofstream &fout, XCAP::Register reg, int writeValue, Endianness e) |

| Generate the encoding for writing a CAP register and write it to file ofstream. More... | |

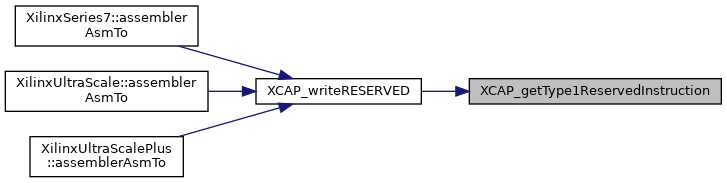

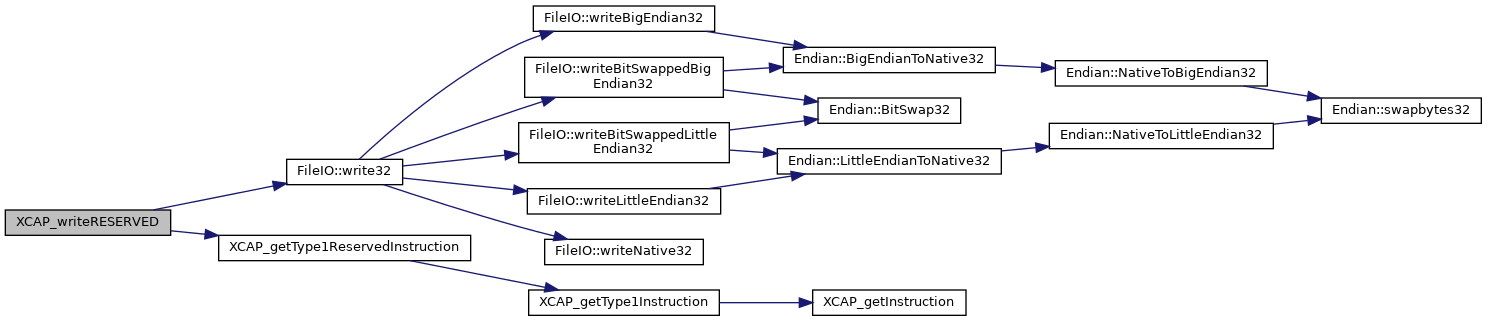

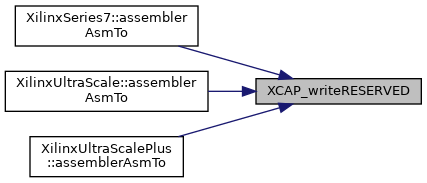

| void | XCAP_writeRESERVED (std::ofstream &fout, int cnt, int payload, Endianness e) |

| Generate the encoding for Reserved instructions and write them to file ofstream. More... | |

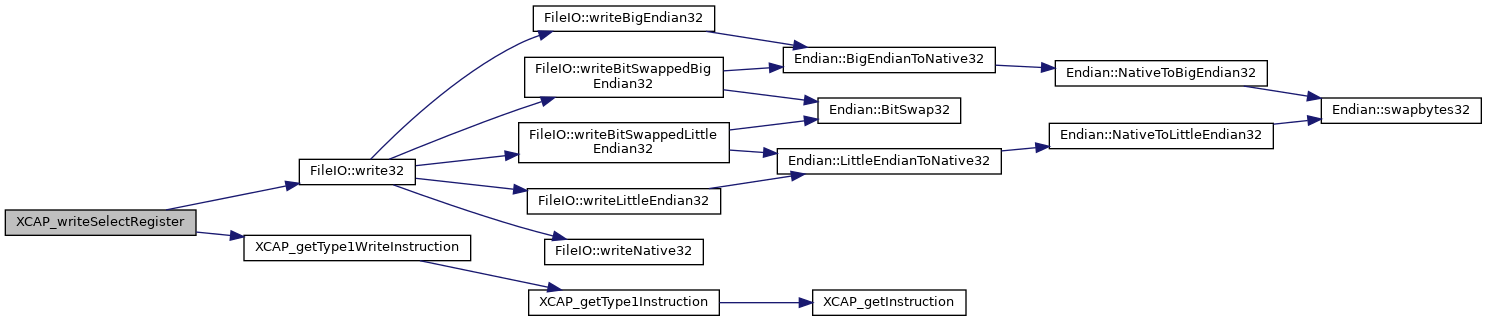

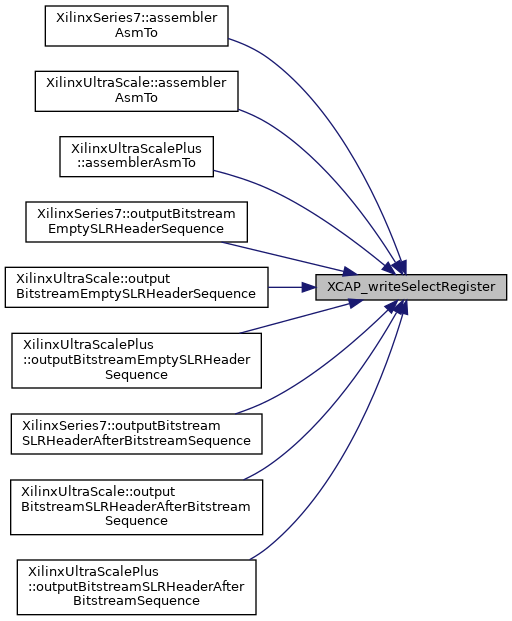

| void | XCAP_writeSelectRegister (std::ofstream &fout, XCAP::Register reg, Endianness e) |

| Generate the encoding for "selecting" a CAP register and write it to file ofstream. More... | |

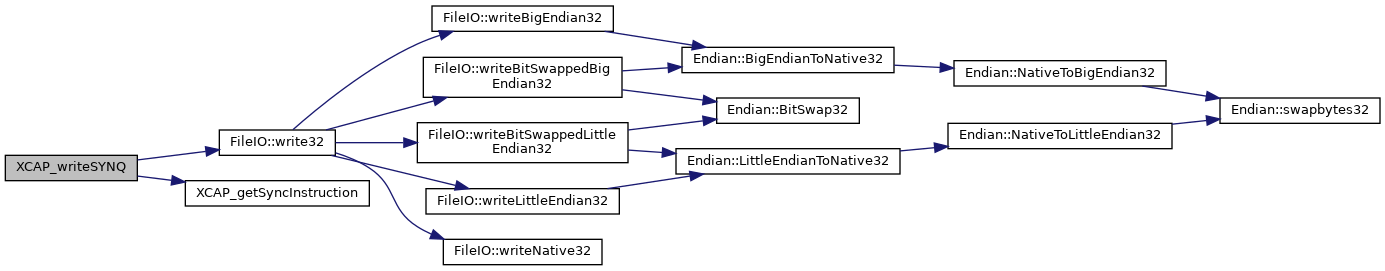

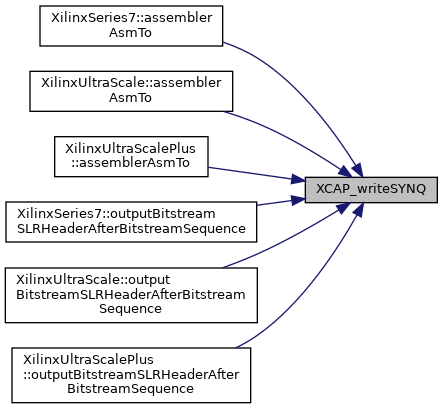

| void | XCAP_writeSYNQ (std::ofstream &fout, Endianness e) |

| Generate and write an SYNQ command. More... | |

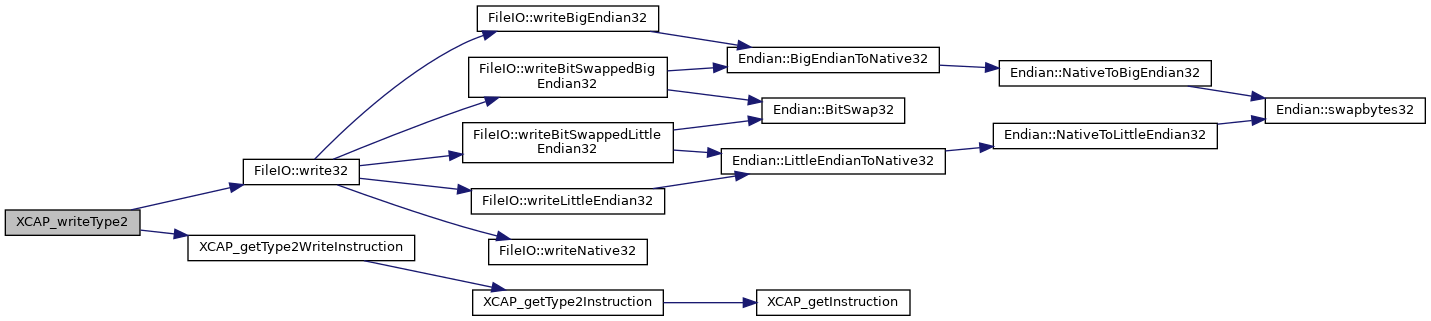

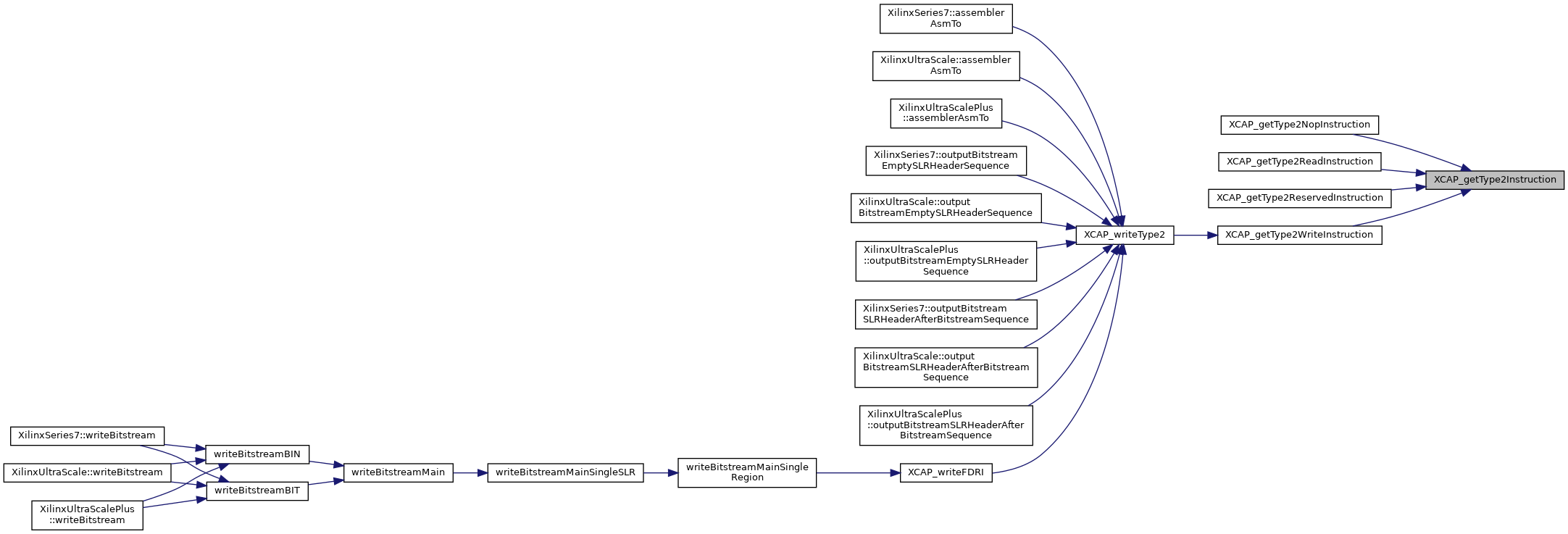

| void | XCAP_writeType2 (std::ofstream &fout, int wordCount, Endianness e) |

| Generate and write only a type 2 FDRI command. More... | |

| #define FABRIC_SYNC_WORD 0xAA995566 |

Definition at line 17 of file inlineCAP.h.

|

strong |

| Enumerator | |

|---|---|

| Phase1 | |

| Phase2 | |

| Phase3 | |

| Phase4 | |

| Phase5 | |

| Phase6 | |

Definition at line 441 of file inlineCAP.h.

|

strong |

| Enumerator | |

|---|---|

| Phase1 | |

| Phase2 | |

| Phase3 | |

| Phase4 | |

| Phase5 | |

| Phase6 | |

| GTS_DONE | GTS tracks DONE pin. Bitstream property: GTS_CYCLE:DONE. |

Definition at line 472 of file inlineCAP.h.

|

strong |

| Enumerator | |

|---|---|

| Phase1 | |

| Phase2 | |

| Phase3 | |

| Phase4 | |

| Phase5 | |

| Phase6 | |

| GWE_DONE | GWE tracks DONE pin. Bitstream property: GWE_CYCLE:DONE. |

Definition at line 482 of file inlineCAP.h.

|

strong |

| Enumerator | |

|---|---|

| Phase0 | |

| Phase1 | |

| Phase2 | |

| Phase3 | |

| Phase4 | |

| Phase5 | |

| Phase6 | |

| NoWait | |

Definition at line 461 of file inlineCAP.h.

|

strong |

| Enumerator | |

|---|---|

| Phase0 | |

| Phase1 | |

| Phase2 | |

| Phase3 | |

| Phase4 | |

| Phase5 | |

| Phase6 | |

| NoWait | |

Definition at line 450 of file inlineCAP.h.

|

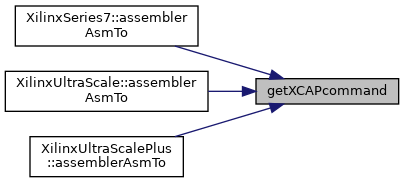

inline |

Definition at line 67 of file inlineCAP.h.

References XCAP::AGHIGH, XCAP::BSPI_READ, XCAP::CRCC, XCAP::DESYNC, XCAP::DGHIGH, XCAP::FALL_EDGE, XCAP::GRESTORE, XCAP::IPROG, XCAP::LTIMER, XCAP::MAGIC2, XCAP::MFW, XCAP::NULLCMD, XCAP::RCFG, XCAP::RCRC, XCAP::SHUTDOWN, XCAP::START, str::iff::stringContains(), XCAP::SWITCH, XCAP::UNDEFINED, XCAP::URAM, and XCAP::WCFG.

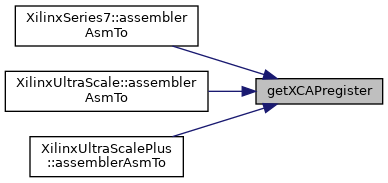

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), and XilinxUltraScalePlus::assemblerAsmTo().

|

inline |

Definition at line 19 of file inlineCAP.h.

References XCAP::AXSS, XCAP::BOOTSTS, XCAP::BSPI, XCAP::CBC, XCAP::COR0, XCAP::COR1, XCAP::CRC, XCAP::CTRL0, XCAP::CTRL1, XCAP::FAR, XCAP::FDRI, XCAP::FDRO, XCAP::IDCODE, XCAP::LOUT, XCAP::MAGIC0, XCAP::MAGIC1, XCAP::MASK, XCAP::MFWR, XCAP::STAT, str::iff::stringContains(), XCAP::TIMER, XCAP::UNDEFINED, and XCAP::WBSTAR.

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), and XilinxUltraScalePlus::assemblerAsmTo().

|

inline |

Definition at line 111 of file inlineCAP.h.

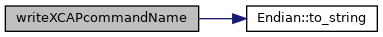

References XCAP::AGHIGH, XCAP::BSPI_READ, XCAP::CRCC, XCAP::DESYNC, XCAP::DGHIGH, XCAP::FALL_EDGE, XCAP::GRESTORE, XCAP::IPROG, XCAP::LTIMER, XCAP::MAGIC2, XCAP::MFW, XCAP::NULLCMD, XCAP::RCFG, XCAP::RCRC, XCAP::SHUTDOWN, XCAP::START, XCAP::SWITCH, Endian::to_string(), XCAP::URAM, and XCAP::WCFG.

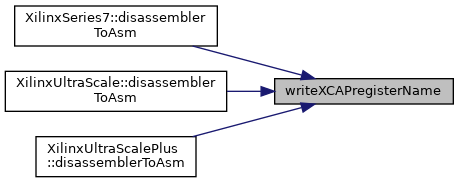

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), and XilinxUltraScalePlus::disassemblerToAsm().

|

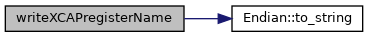

inline |

Definition at line 177 of file inlineCAP.h.

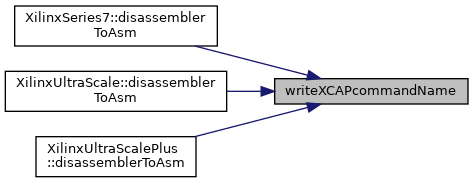

References XCAP::AXSS, XCAP::BOOTSTS, XCAP::BSPI, XCAP::CBC, XCAP::CMD, XCAP::COR0, XCAP::COR1, XCAP::CRC, XCAP::CTRL0, XCAP::CTRL1, XCAP::FAR, XCAP::FDRI, XCAP::FDRO, XCAP::IDCODE, XCAP::LOUT, XCAP::MAGIC0, XCAP::MAGIC1, XCAP::MASK, XCAP::MFWR, XCAP::STAT, XCAP::TIMER, Endian::to_string(), and XCAP::WBSTAR.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), and XilinxUltraScalePlus::disassemblerToAsm().

|

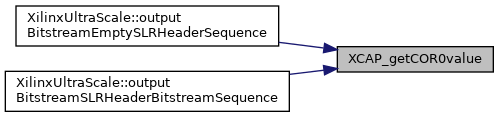

inline |

Generate COR0 register write value.

Definition at line 493 of file inlineCAP.h.

Referenced by XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), and XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence().

|

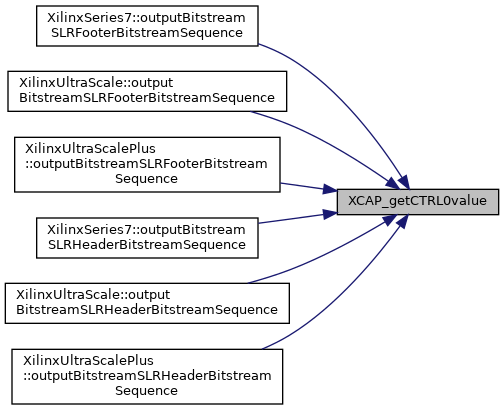

inline |

Generate CTRL0 register write value.

Definition at line 513 of file inlineCAP.h.

Referenced by XilinxSeries7::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRFooterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence(), and XilinxUltraScalePlus::outputBitstreamSLRHeaderBitstreamSequence().

|

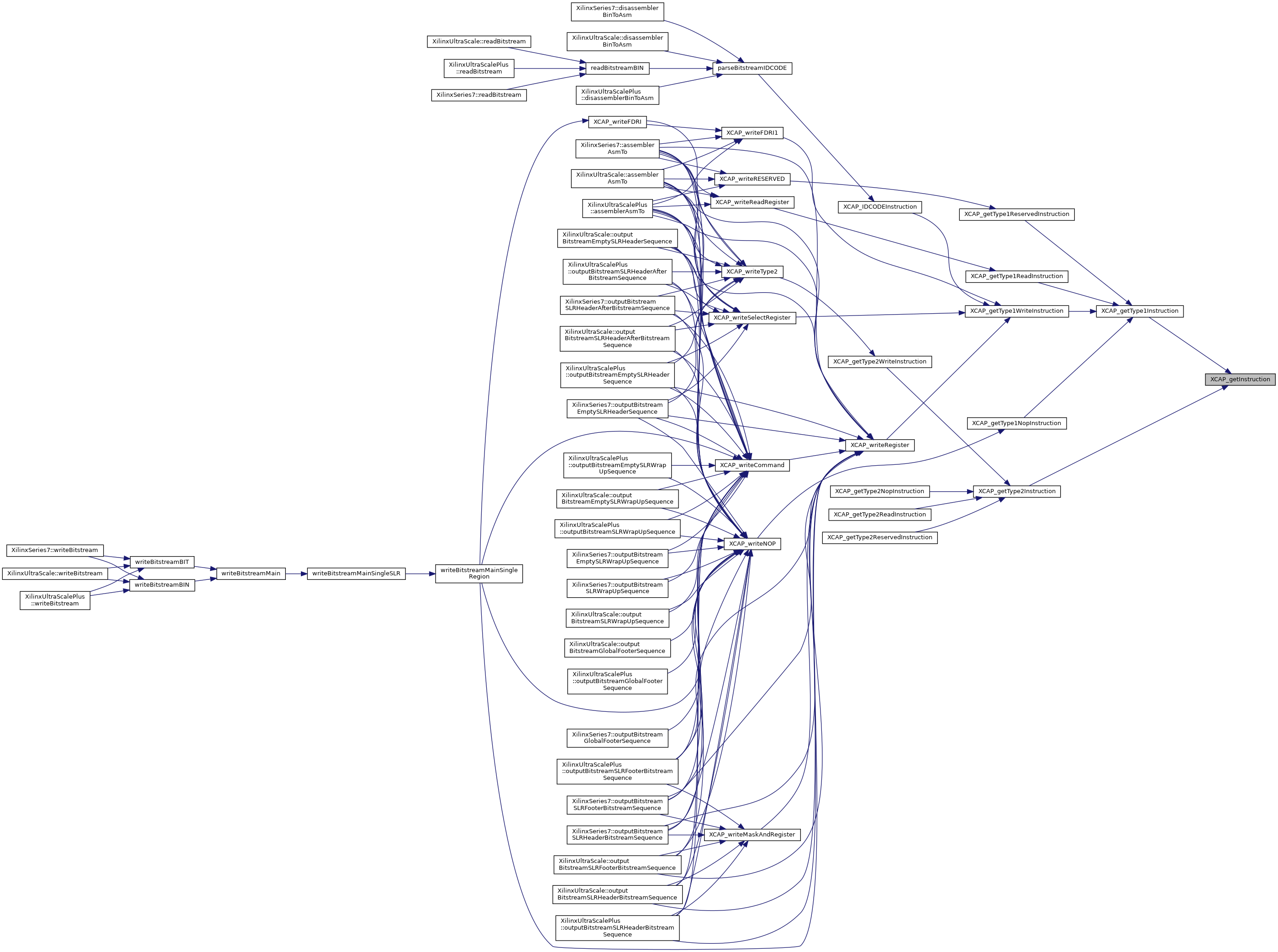

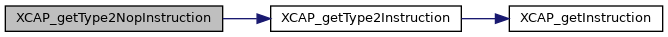

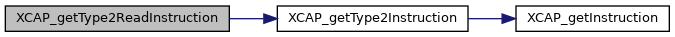

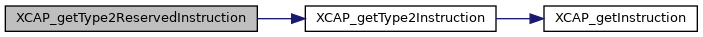

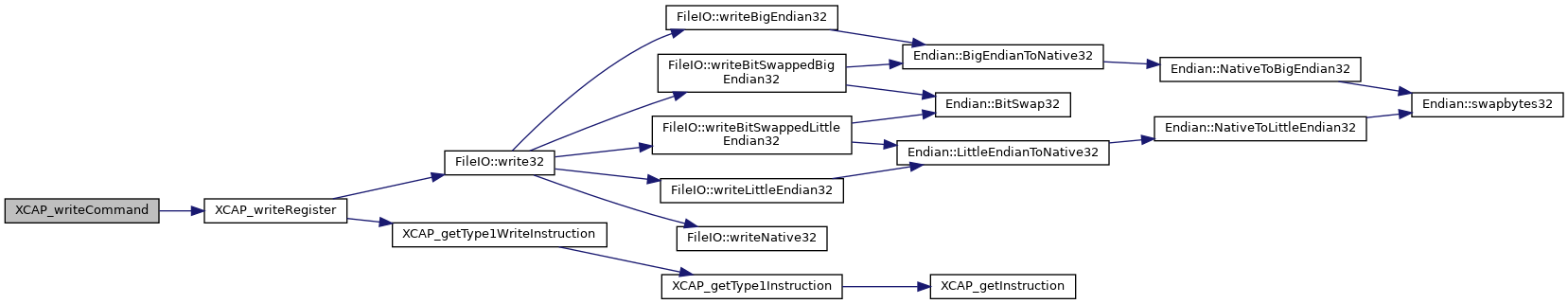

inline |

Generate and return the encoding for an instruction.

Definition at line 283 of file inlineCAP.h.

Referenced by XCAP_getType1Instruction(), and XCAP_getType2Instruction().

|

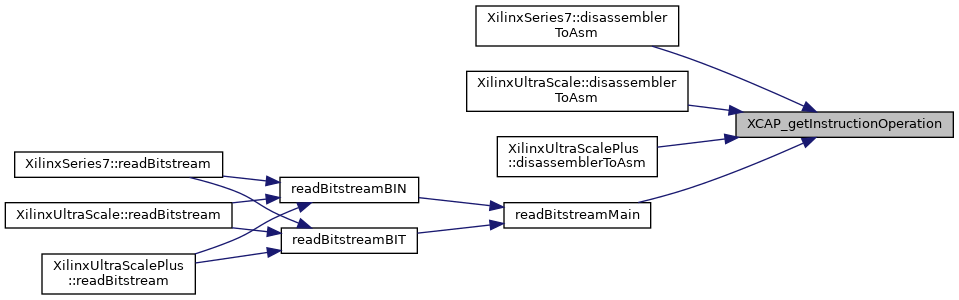

inline |

Parses and returns instruction operation. Most Xil instructions will NOP or write.

Definition at line 259 of file inlineCAP.h.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), XilinxUltraScalePlus::disassemblerToAsm(), and readBitstreamMain().

|

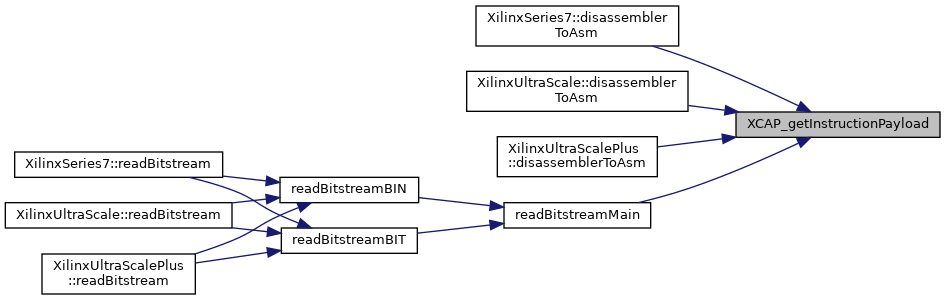

inline |

Parses and returns instruction payload. This is the immediate value after instruction type and operation encodings.

Definition at line 265 of file inlineCAP.h.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), XilinxUltraScalePlus::disassemblerToAsm(), and readBitstreamMain().

|

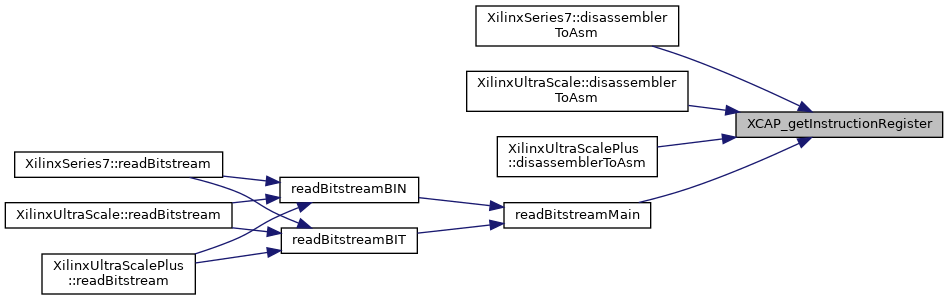

inline |

Parses and returns instruction register. This is the register being addressed if the instruction is of type 1.

Definition at line 271 of file inlineCAP.h.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), XilinxUltraScalePlus::disassemblerToAsm(), and readBitstreamMain().

|

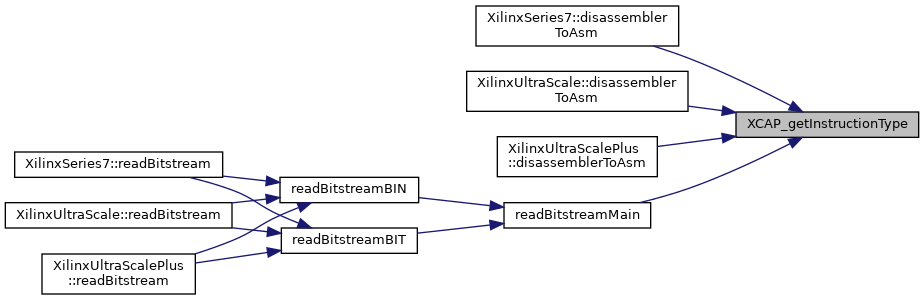

inline |

Parses and returns instruction type. Valid Xil instructions will be of types 1 and 2.

Definition at line 253 of file inlineCAP.h.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), XilinxUltraScalePlus::disassemblerToAsm(), and readBitstreamMain().

|

inline |

Parses and returns instruction word count. This is the number of words to be read/written if the instruction is of type 1.

Definition at line 277 of file inlineCAP.h.

Referenced by XilinxSeries7::disassemblerToAsm(), XilinxUltraScale::disassemblerToAsm(), XilinxUltraScalePlus::disassemblerToAsm(), and readBitstreamMain().

|

inline |

Generate and return the encoding for a SYNC instruction.

Definition at line 430 of file inlineCAP.h.

References FABRIC_SYNC_WORD.

Referenced by findBitstreamSyncSequence(), findBitstreamSyncWord(), outputCAPheaderConstant(), parseBitstreamEndianness(), and XCAP_writeSYNQ().

|

inline |

Generate and return the encoding for a type 1 instruction.

Definition at line 292 of file inlineCAP.h.

References XCAP_getInstruction().

Referenced by XCAP_getType1NopInstruction(), XCAP_getType1ReadInstruction(), XCAP_getType1ReservedInstruction(), and XCAP_getType1WriteInstruction().

|

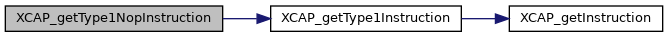

inline |

Generate and return the encoding for a type 1 NOP instruction.

Definition at line 298 of file inlineCAP.h.

References XCAP::NOP, and XCAP_getType1Instruction().

Referenced by XCAP_writeNOP().

|

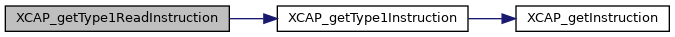

inline |

Generate and return the encoding for a type 1 Read instruction.

Definition at line 304 of file inlineCAP.h.

References XCAP::READ, and XCAP_getType1Instruction().

Referenced by XCAP_writeReadRegister().

|

inline |

Generate and return the encoding for a type 1 Reserved instruction.

Definition at line 316 of file inlineCAP.h.

References XCAP::RESERVED, and XCAP_getType1Instruction().

Referenced by XCAP_writeRESERVED().

|

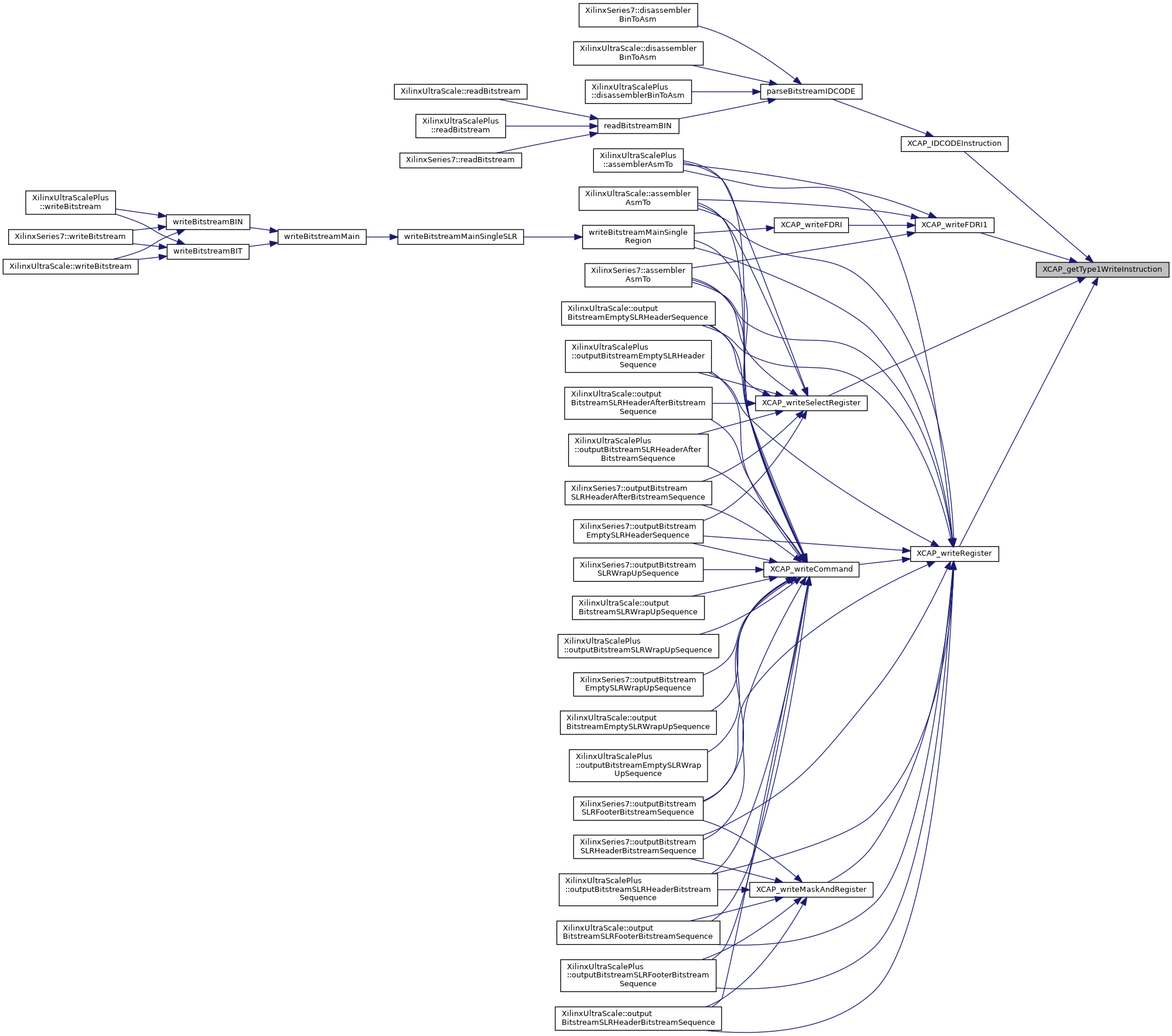

inline |

Generate and return the encoding for a type 1 Write instruction.

Definition at line 310 of file inlineCAP.h.

References XCAP::WRITE, and XCAP_getType1Instruction().

Referenced by XCAP_IDCODEInstruction(), XCAP_writeFDRI1(), XCAP_writeRegister(), and XCAP_writeSelectRegister().

|

inline |

Generate and return the encoding for a type 2 instruction.

Definition at line 322 of file inlineCAP.h.

References XCAP_getInstruction().

Referenced by XCAP_getType2NopInstruction(), XCAP_getType2ReadInstruction(), XCAP_getType2ReservedInstruction(), and XCAP_getType2WriteInstruction().

|

inline |

Generate and return the encoding for a type 2 NOP instruction.

Definition at line 328 of file inlineCAP.h.

References XCAP::NOP, and XCAP_getType2Instruction().

|

inline |

Generate and return the encoding for a type 2 Read instruction.

Definition at line 334 of file inlineCAP.h.

References XCAP::READ, and XCAP_getType2Instruction().

|

inline |

Generate and return the encoding for a type 2 Reserved instruction.

Definition at line 346 of file inlineCAP.h.

References XCAP::RESERVED, and XCAP_getType2Instruction().

|

inline |

Generate and return the encoding for a type 2 Write instruction.

Definition at line 340 of file inlineCAP.h.

References XCAP::WRITE, and XCAP_getType2Instruction().

Referenced by XCAP_writeType2().

|

inline |

Generate and return the encoding for a IDCODE writing instruction.

Definition at line 424 of file inlineCAP.h.

References XCAP::IDCODE, and XCAP_getType1WriteInstruction().

Referenced by parseBitstreamIDCODE().

|

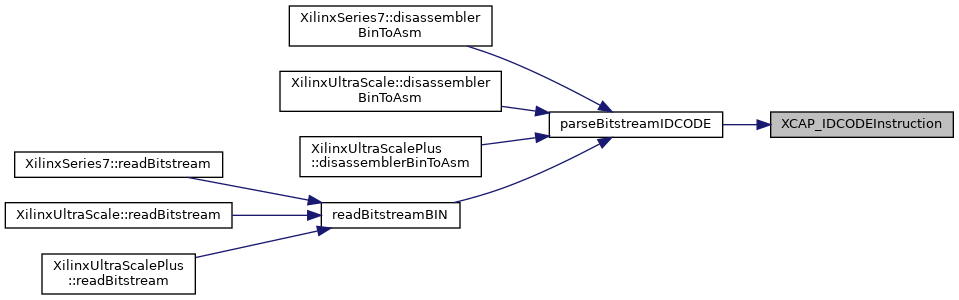

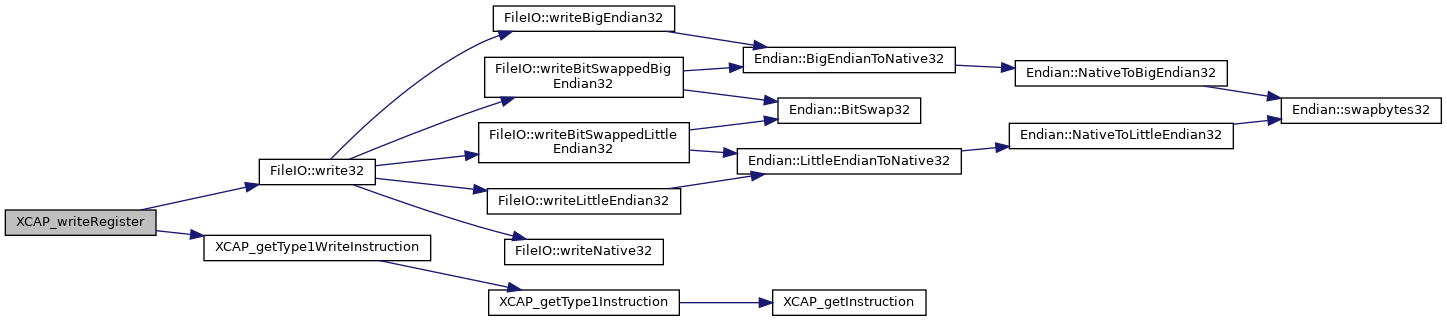

inline |

Generate the encoding for writing a CAP command and write it to file ofstream.

Definition at line 390 of file inlineCAP.h.

References XCAP::CMD, and XCAP_writeRegister().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRHeaderSequence(), XilinxSeries7::outputBitstreamEmptySLRWrapUpSequence(), XilinxUltraScale::outputBitstreamEmptySLRWrapUpSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRWrapUpSequence(), XilinxSeries7::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRFooterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderBitstreamSequence(), XilinxSeries7::outputBitstreamSLRWrapUpSequence(), XilinxUltraScale::outputBitstreamSLRWrapUpSequence(), XilinxUltraScalePlus::outputBitstreamSLRWrapUpSequence(), and writeBitstreamMainSingleRegion().

|

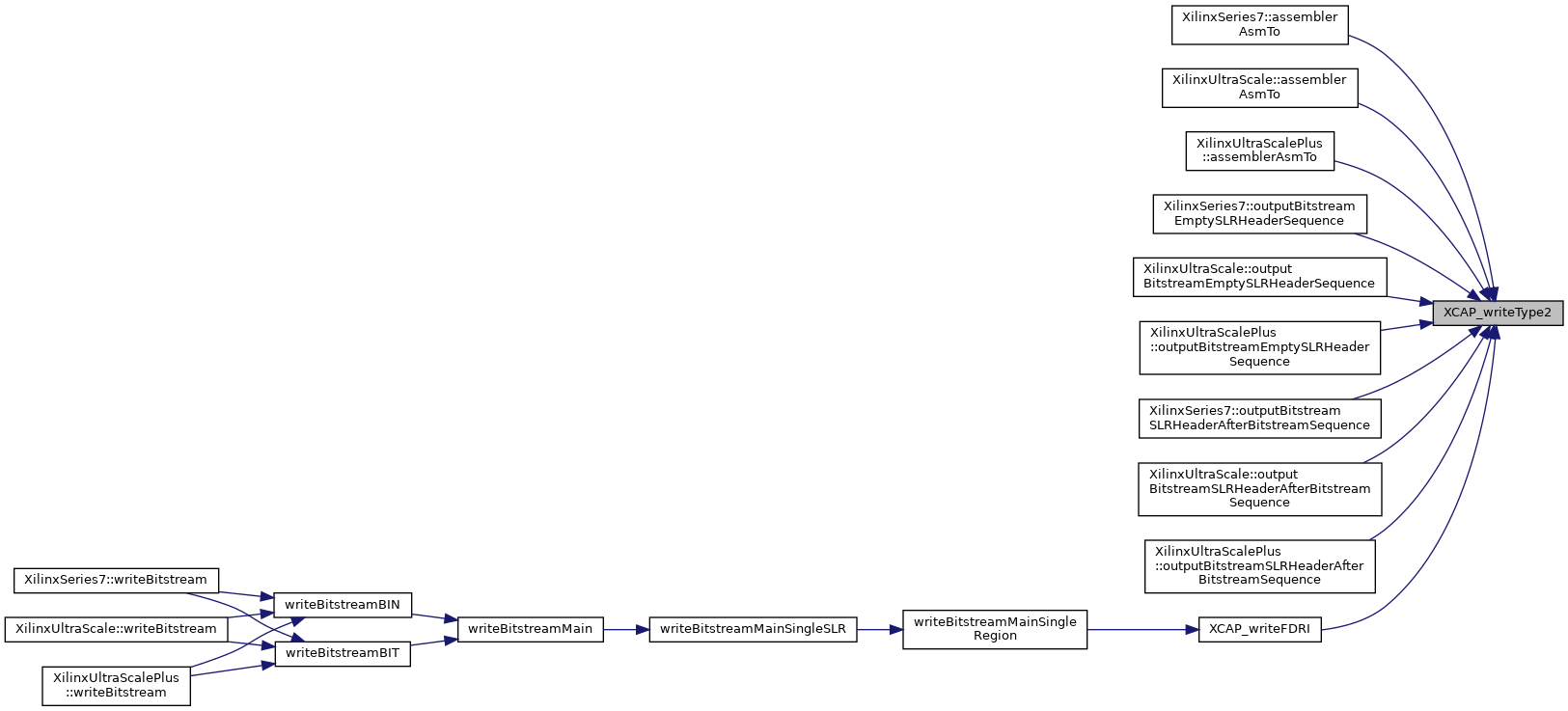

inline |

Generate and write an FDRI command. Always uses type 2 command for simplicity.

Definition at line 417 of file inlineCAP.h.

References XCAP_writeFDRI1(), and XCAP_writeType2().

Referenced by writeBitstreamMainSingleRegion().

|

inline |

Generate and write only a type 1 FDRI command.

Definition at line 403 of file inlineCAP.h.

References XCAP::FDRI, FileIO::write32(), and XCAP_getType1WriteInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), and XCAP_writeFDRI().

|

inline |

Generate the encoding for writing a CAP register with a mask and write it to file ofstream.

Definition at line 396 of file inlineCAP.h.

References XCAP::MASK, and XCAP_writeRegister().

Referenced by XilinxSeries7::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRFooterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence(), and XilinxUltraScalePlus::outputBitstreamSLRHeaderBitstreamSequence().

|

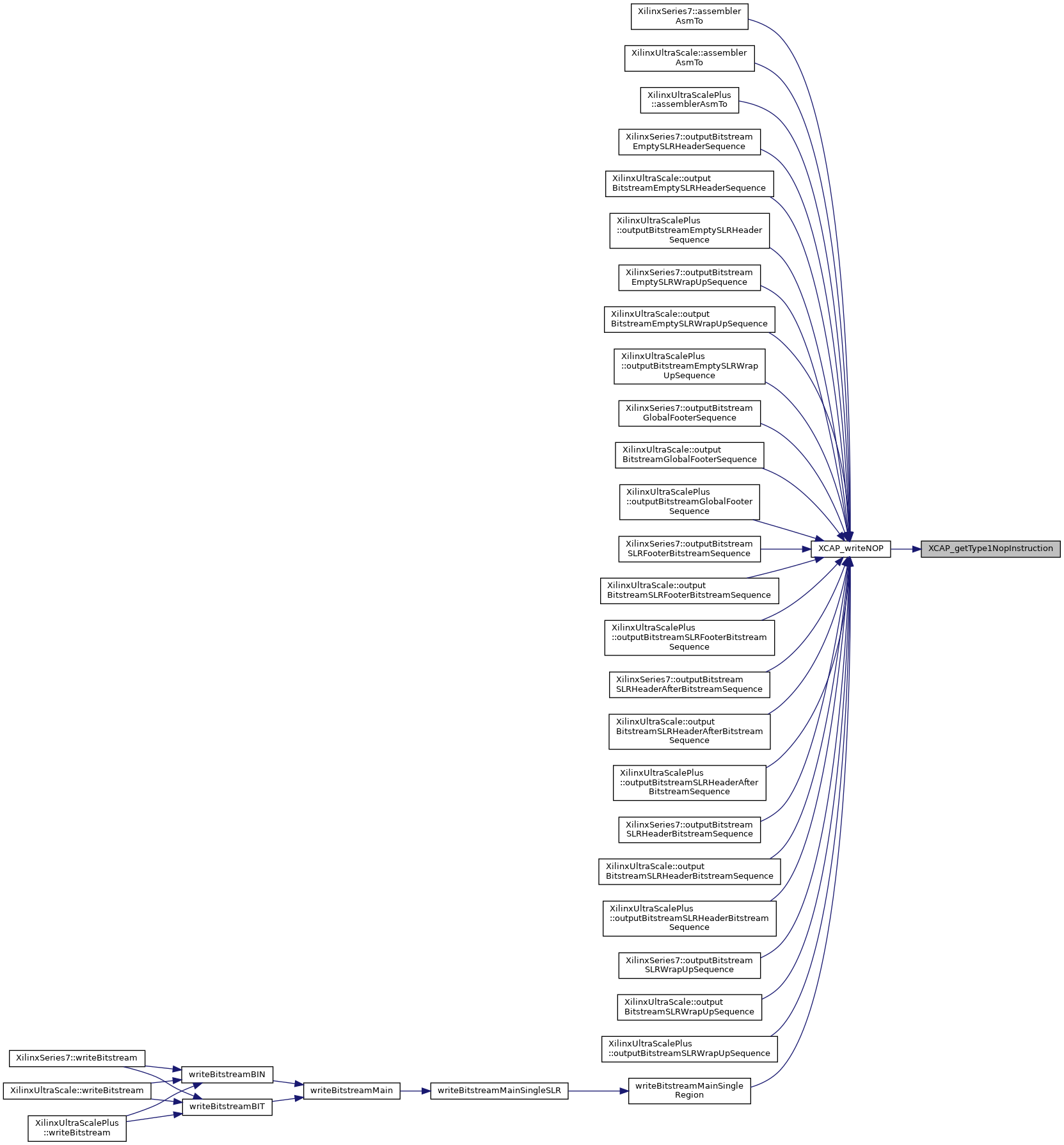

inline |

Generate the encoding for NOP instructions and write them to file ofstream.

Definition at line 352 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType1NopInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRHeaderSequence(), XilinxSeries7::outputBitstreamEmptySLRWrapUpSequence(), XilinxUltraScale::outputBitstreamEmptySLRWrapUpSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRWrapUpSequence(), XilinxSeries7::outputBitstreamGlobalFooterSequence(), XilinxUltraScale::outputBitstreamGlobalFooterSequence(), XilinxUltraScalePlus::outputBitstreamGlobalFooterSequence(), XilinxSeries7::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRFooterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderBitstreamSequence(), XilinxSeries7::outputBitstreamSLRWrapUpSequence(), XilinxUltraScale::outputBitstreamSLRWrapUpSequence(), XilinxUltraScalePlus::outputBitstreamSLRWrapUpSequence(), and writeBitstreamMainSingleRegion().

|

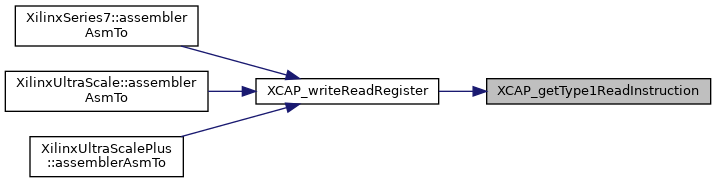

inline |

Generate the encoding for reading a CAP register and write it to file ofstream.

Definition at line 375 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType1ReadInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), and XilinxUltraScalePlus::assemblerAsmTo().

|

inline |

Generate the encoding for writing a CAP register and write it to file ofstream.

Definition at line 382 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType1WriteInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRHeaderSequence(), XilinxSeries7::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRFooterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRFooterBitstreamSequence(), XilinxSeries7::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderBitstreamSequence(), writeBitstreamMainSingleRegion(), XCAP_writeCommand(), and XCAP_writeMaskAndRegister().

|

inline |

Generate the encoding for Reserved instructions and write them to file ofstream.

Definition at line 360 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType1ReservedInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), and XilinxUltraScalePlus::assemblerAsmTo().

|

inline |

Generate the encoding for "selecting" a CAP register and write it to file ofstream.

Definition at line 368 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType1WriteInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRHeaderSequence(), XilinxSeries7::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderAfterBitstreamSequence(), and XilinxUltraScalePlus::outputBitstreamSLRHeaderAfterBitstreamSequence().

|

inline |

Generate and write an SYNQ command.

Definition at line 436 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getSyncInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderAfterBitstreamSequence(), and XilinxUltraScalePlus::outputBitstreamSLRHeaderAfterBitstreamSequence().

|

inline |

Generate and write only a type 2 FDRI command.

Definition at line 410 of file inlineCAP.h.

References FileIO::write32(), and XCAP_getType2WriteInstruction().

Referenced by XilinxSeries7::assemblerAsmTo(), XilinxUltraScale::assemblerAsmTo(), XilinxUltraScalePlus::assemblerAsmTo(), XilinxSeries7::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScale::outputBitstreamEmptySLRHeaderSequence(), XilinxUltraScalePlus::outputBitstreamEmptySLRHeaderSequence(), XilinxSeries7::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScale::outputBitstreamSLRHeaderAfterBitstreamSequence(), XilinxUltraScalePlus::outputBitstreamSLRHeaderAfterBitstreamSequence(), and XCAP_writeFDRI().