About rFAS

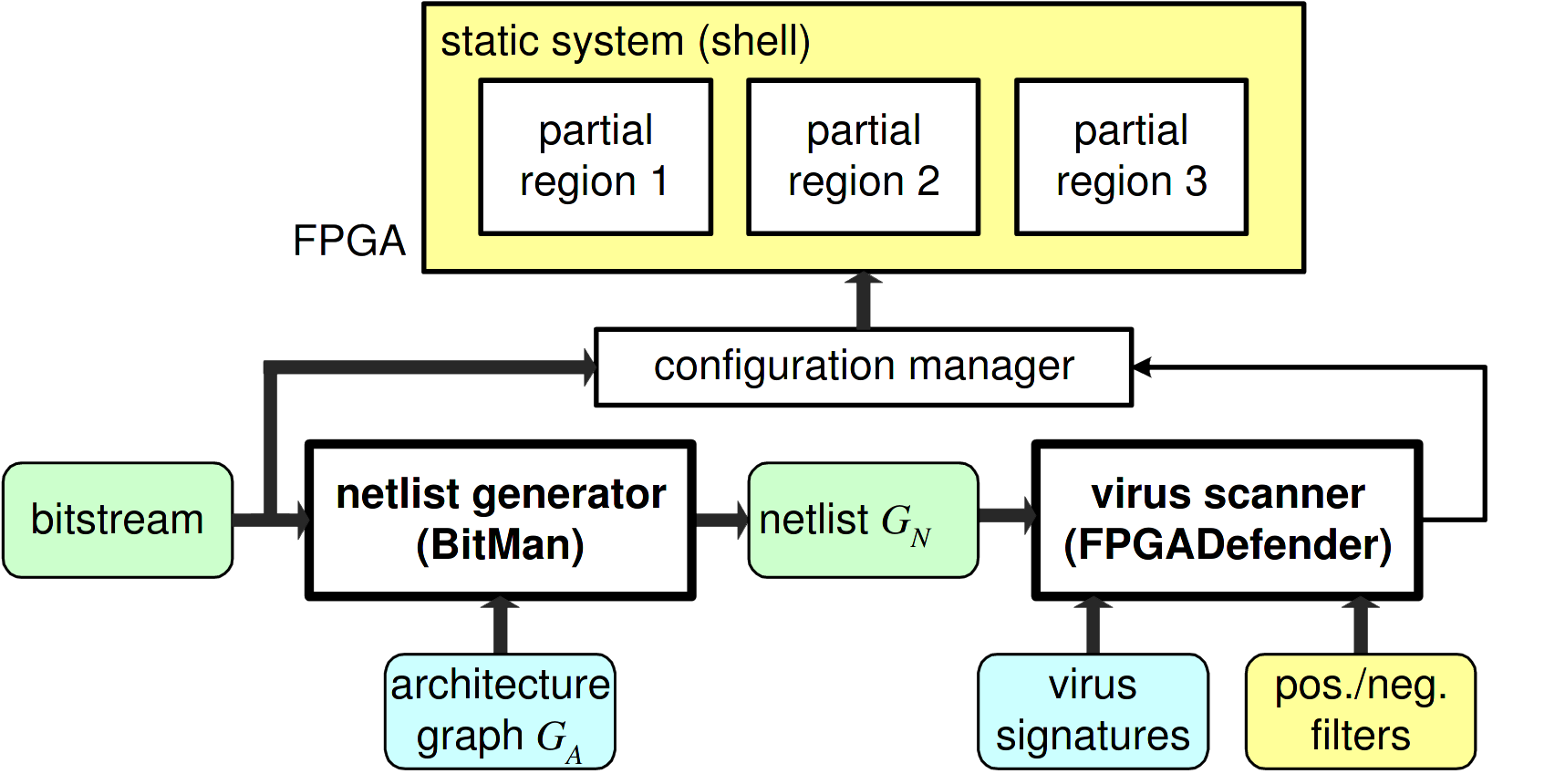

FPGAs are ideal for number crunching problems that fit dataflow processing model. With accelerator sandboxing the FPGAs provide a platform for executing these models. This platform is developed in the FOS - FPGA Operating System project.

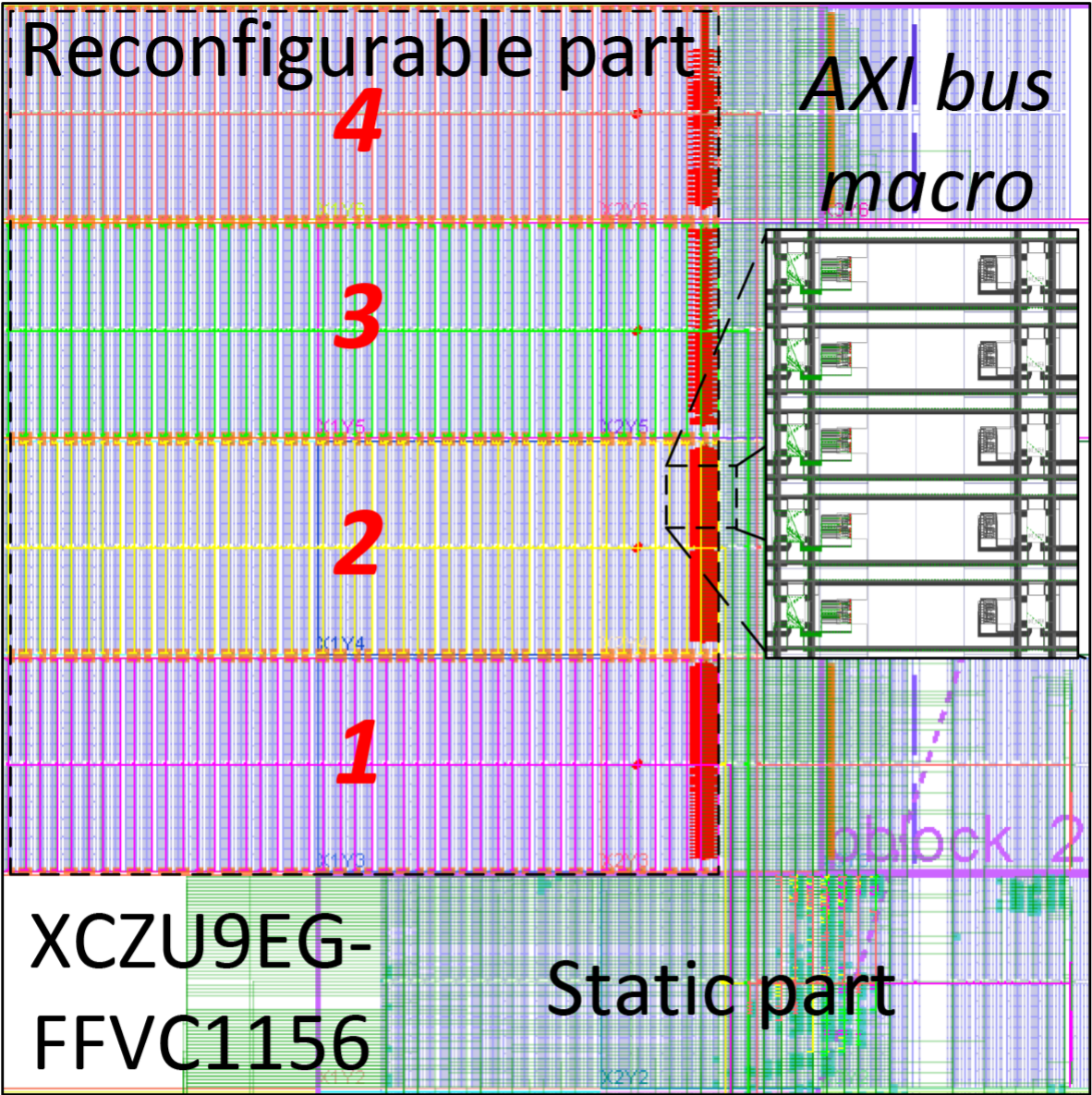

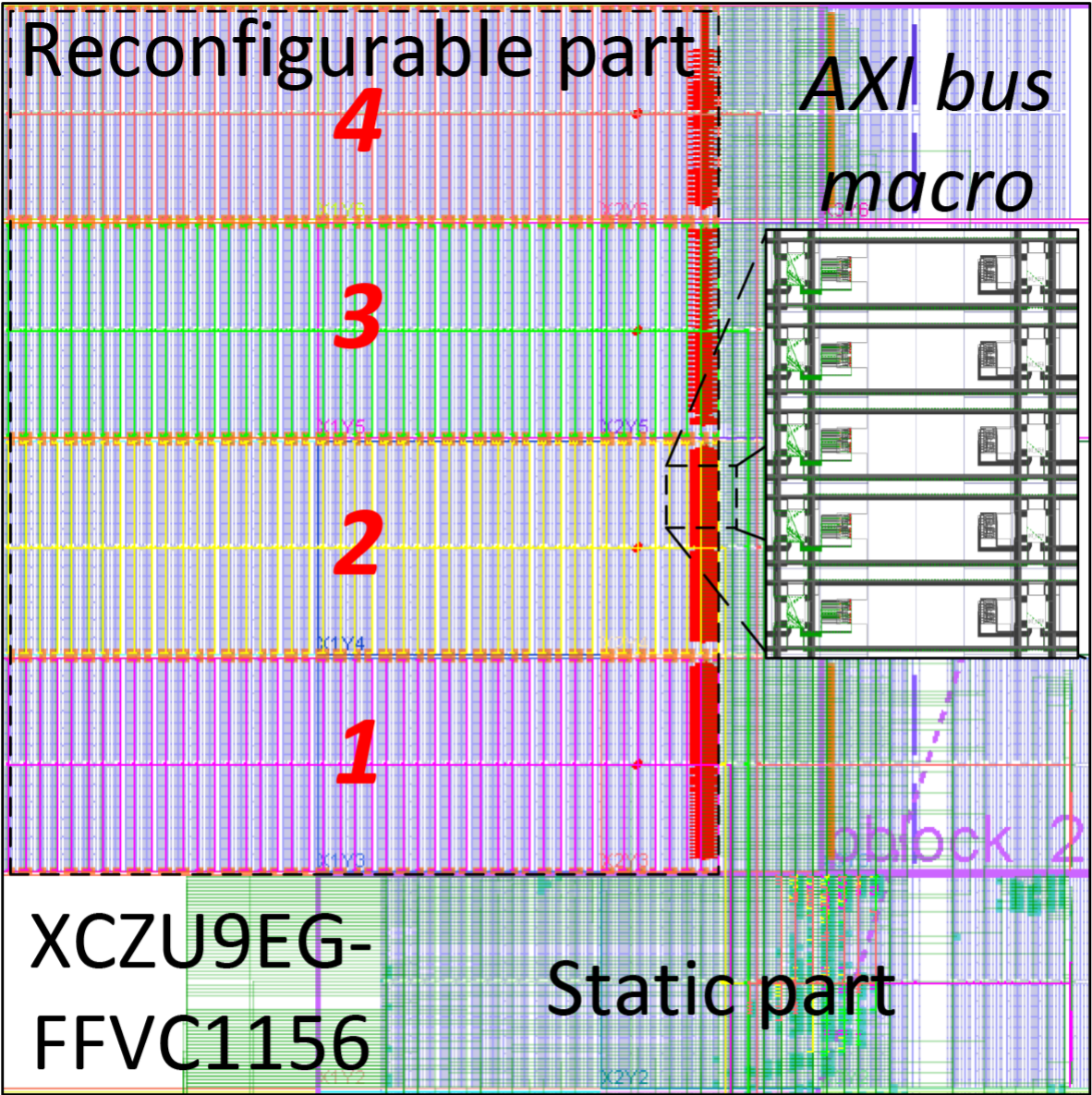

Reconfigurable FPGA Accelerator Sandboxing